您當(dāng)前的位置:檢測資訊 > 科研開發(fā)

嘉峪檢測網(wǎng) 2025-09-03 19:58

在做MCU選型時(shí),很多工程師可能會(huì)重點(diǎn)關(guān)注芯片的靜電指標(biāo)作為產(chǎn)品設(shè)計(jì)的重要參考。

那么,問題來了。

如果你要做一款滿足產(chǎn)品接觸8KV,空氣放電15KV的產(chǎn)品,是不是選一顆HBM靜電為2KV的芯片就一定比1KV的更好?

為了搞清楚這個(gè)問題,我們按以下幾點(diǎn)拆解:

1)芯片的靜電和產(chǎn)品靜電的區(qū)別。

2)正常的產(chǎn)品生產(chǎn)工藝,芯片的靜電指標(biāo)要求是多少?

3)從芯片規(guī)格書來看芯片靜電和產(chǎn)品靜電的對應(yīng)關(guān)系。

4)從實(shí)際數(shù)據(jù)來看芯片靜電和產(chǎn)品靜電的對應(yīng)關(guān)系。

5)為什么芯片HBM指標(biāo)越高,產(chǎn)品靜電并不一定更好?

下面分別說明:

1、芯片的靜電和產(chǎn)品靜電的區(qū)別。

芯片靜電:

要了解芯片靜電,最直接的辦法就是看芯片的規(guī)格書上寫了啥。

比如,這款STM8AF5268TCY的規(guī)格書給出了芯片靜電的各項(xiàng)指標(biāo),包括HBM,CDM和MM。

需要補(bǔ)充說明的是,MM靜電測試現(xiàn)在并不是強(qiáng)制測試要求,因此現(xiàn)在大部分芯片的規(guī)格書只能看到HBM和CDM的測試數(shù)據(jù)。

芯片靜電的設(shè)計(jì)目的是芯片在生產(chǎn)、運(yùn)輸和組裝過程中避免因?yàn)殪o電導(dǎo)致?lián)p壞,芯片靜電測試是在芯片不加電的條件下進(jìn)行測試的。

HBM靜電(Human Body Model,人體放電模型)是靜電放電(ESD)測試中最常用的模型之一,用于模擬人體接觸電子器件時(shí)因靜電積累導(dǎo)致的放電現(xiàn)象。

芯片的HBM測試簡圖如下,簡單理解就是100pF電容通過1.5K電阻對芯片管腳放電。

CDM靜電(Charged-Device Model,充電器件模型)是芯片靜電放電的另一種模式,用于模擬電子器件在生產(chǎn)、運(yùn)輸或使用過程中因摩擦或感應(yīng)帶電后,通過引腳對地放電的場景。

產(chǎn)品系統(tǒng)級(jí)靜電:

系統(tǒng)級(jí)靜電(System-Level ESD)是指電子設(shè)備在終端使用環(huán)境中因人體接觸、摩擦或外部電場作用產(chǎn)生的靜電放電現(xiàn)象,其防護(hù)重點(diǎn)在于整機(jī)或系統(tǒng)而非單個(gè)芯片,測試標(biāo)準(zhǔn)為IEC61000-4-2,系統(tǒng)級(jí)靜電又分接觸式和空氣式兩種方法。

系統(tǒng)級(jí)靜電的測試簡圖如下,簡單理解就是150pF電容通過330歐姆電阻對產(chǎn)品放電。

兩種標(biāo)準(zhǔn)的放電電阻差異較大,導(dǎo)致放電的峰值電流差異也較大,對比如下表:

簡單理解就是同樣的靜電電壓,系統(tǒng)級(jí)靜電測試更嚴(yán)苛。

2、正常的產(chǎn)品生產(chǎn)工藝,芯片的靜電指標(biāo)要求是多少?

我們再來看TI的一份芯片規(guī)格書上面怎樣寫的。

從上面的信息可以看出,如果在一個(gè)靜電受控的生產(chǎn)環(huán)境,MCU的HBM和CDM指標(biāo)分別為500V和250V就足夠了,至少在生產(chǎn)制造環(huán)節(jié),芯片不會(huì)被損壞。

我們打開JEP155這篇文檔,看看為什么500V的HBM就足夠了。

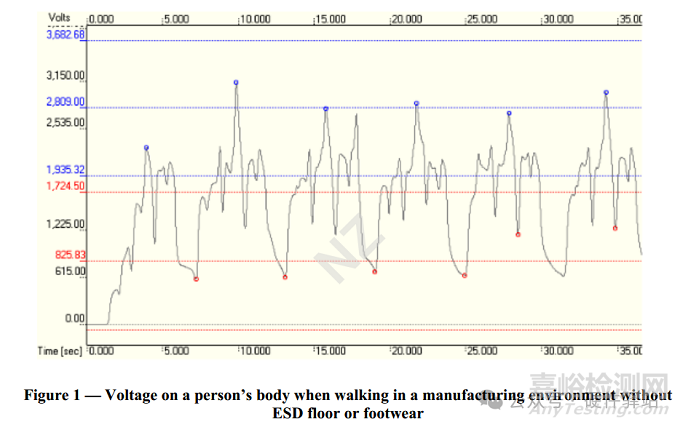

1)假設(shè),剛開始,老板沒錢,工廠不愿意做任何ESD防護(hù),一個(gè)人在不做ESD處理的制造環(huán)境行走,可以產(chǎn)生接近3000V的靜電。

按這個(gè)環(huán)境生產(chǎn)電子產(chǎn)品,一些靜電只有2000V或以下的芯片,就難以避免靜電損壞。一個(gè)可預(yù)期的結(jié)果就是生產(chǎn)的產(chǎn)品會(huì)出現(xiàn)質(zhì)量問題。這個(gè)時(shí)候,老板就得做一下整改。

2)先投點(diǎn)小錢,把工廠的地板改造為防靜電的,這個(gè)時(shí)候,員工測試ESD的數(shù)值如下:

可以看出,加了錢就是不一樣,靜電從3000V掉到了260V以下,這個(gè)環(huán)境對所有芯片靜電指標(biāo)為500V以上的已經(jīng)足夠友好了。

但是,某一天,來了一個(gè)客戶要求生產(chǎn)組裝一款包含有GaAs工藝的放大器芯片產(chǎn)品,此芯片的HBM ESD只有250V,這個(gè)時(shí)候,老板又考慮了一下,還得加錢。

3)于是所有的員工都穿上了防靜電鞋,帶上防靜電手環(huán),員工測試ESD的數(shù)值如下:

靜電電壓從260V掉到了不超過40V,這下老板再也不擔(dān)心工廠的靜電問題了。

以上就是有關(guān)芯片HBM指標(biāo)為什么設(shè)計(jì)為500V就可以確保生產(chǎn)中不被損壞的詳細(xì)解釋,CDM的相關(guān)說明大家可以參考JEP157文檔說明,不再贅述。

3、從芯片規(guī)格書來看芯片靜電和產(chǎn)品靜電的對應(yīng)關(guān)系。

我們繼續(xù),下面講一下MCU的HBM靜電和系統(tǒng)靜電是否有相關(guān)性,說得更直白一點(diǎn)就是我選的MCU靜電指標(biāo)越高,是不是做出來的產(chǎn)品靜電指標(biāo)就更好。

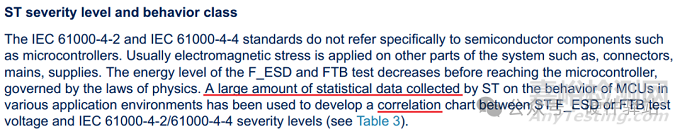

意法半導(dǎo)體的一篇文檔AN1709對此進(jìn)行了相關(guān)說明。提出了一項(xiàng)指標(biāo)叫FESD,就是采用系統(tǒng)級(jí)的靜電槍測試芯片管腳,標(biāo)準(zhǔn)不再是HBM,而是IEC61000-4-2。

通過大量數(shù)據(jù)搜集,ST還給出了該指標(biāo)用于產(chǎn)品上的系統(tǒng)指標(biāo)對照列表如下:

比如說,用一個(gè)IEC61000-4-2的靜電槍打芯片,測試芯片1.2KV PASS,1.5KV FAIL,那么這顆MCU在產(chǎn)品上預(yù)計(jì)能夠達(dá)到系統(tǒng)級(jí)的等級(jí)3水平,也就是接觸6KV。

另外需要補(bǔ)充一點(diǎn)的就是,系統(tǒng)級(jí)靜電的測試標(biāo)準(zhǔn)除了電壓等級(jí)之外,失效模式分類也更復(fù)雜。一共4類。

A類最牛,靜電測試時(shí)啥影響都沒有。

B類也還行,系統(tǒng)打復(fù)位或死機(jī)(開啟了看門狗后可恢復(fù))都算,系統(tǒng)可自行恢復(fù)。

C類和D類就沒啥意思了,沒聽說那家客戶可接受的。

B類的詳細(xì)解釋如下:

為了分析芯片靜電和系統(tǒng)靜電是否有關(guān)系,隨機(jī)找了ST的各類型MCU芯片的指標(biāo)對比如下:

備注:芯片型號(hào)是針對某一具體封裝,靜電指標(biāo)是手冊給出的此系列所有芯片的指標(biāo)。

可以看出如下信息:

1)VFESD指標(biāo)大都只給出了等級(jí)B的標(biāo)準(zhǔn)數(shù)據(jù),A等級(jí)的只有一顆芯片數(shù)據(jù)提供。

2)HBM為4000V的,VFESD有2B和3A兩種數(shù)據(jù)。而兩顆HBM為1000V的芯片,VFESD也能達(dá)到3B。

3)HBM一列,有兩顆芯片的Vbat指標(biāo)偏弱。

4)CDM一列,有三顆芯片用不同封裝,指標(biāo)會(huì)下降。

下面分別說明:

1)芯片A等級(jí),意味著更嚴(yán)格的測試標(biāo)準(zhǔn),而B等級(jí)則相對容易達(dá)成一點(diǎn),比如,如果某產(chǎn)品測試時(shí)允許復(fù)位,在開發(fā)中,可以通過軟件的方式做一些處理,在芯片可能導(dǎo)致C類失效前通過軟件提前復(fù)位芯片,提升B類測試的電壓等級(jí)。

芯片規(guī)格書如果未提供A等級(jí)的指標(biāo),而你的產(chǎn)品要求是A等級(jí)的,那就得實(shí)測。

2)從HBM的數(shù)據(jù)和FESD的數(shù)據(jù)關(guān)系來看,兩者并不具備關(guān)聯(lián)性,因此,如果一個(gè)芯片設(shè)計(jì)工程師如果僅僅想依靠提升HBM的數(shù)據(jù)指標(biāo)提高芯片在產(chǎn)品上的靜電性能并不一定是一種很有效的方法,且會(huì)導(dǎo)致芯片成本上升。

下圖是一款芯片從HBM 2KV提升到IEC 8KV的芯片面積對比,供參考。

3)Vbat管腳通常用來外接紐扣電池,需要低功耗設(shè)計(jì),推斷ESD設(shè)計(jì)策略和其它管腳可能存在不同的電路方案。

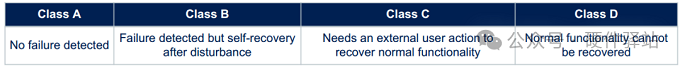

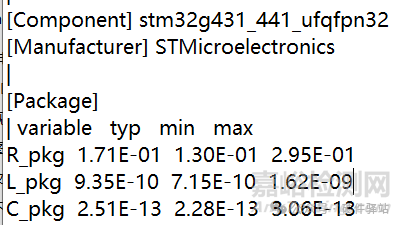

4)CDM測試這一列,有3顆芯片存在CDM的指標(biāo)和封裝具有相關(guān)性,我們拿11行的STM32G491這顆芯片看看有沒有規(guī)律。下劃線紅線的兩種封裝CDM值弱于其它封裝,那就查找一下大封裝的芯片的封裝參數(shù)。

通過IBIS模型提取LQFP100封裝的RLC參數(shù)如下表,電阻在120毫歐左右,電感在6nH左右,并且出現(xiàn)了4個(gè)極值波峰,正好對應(yīng)芯片的4個(gè)邊角。

我們再看看最小封裝UFQFPN32的參數(shù),這個(gè)系列的芯片IBIS模型沒有查到數(shù)據(jù),G431芯片提供了如下參數(shù),可以作為參考。電感值的范圍為0.935nH~1.62nH,比大封裝小不少。

以上只是講了如何通過IBIS模型提取封裝RLC參數(shù),至于CDM測試結(jié)果和封裝有什么關(guān)系,讀者朋友可以自行研究。

從上面芯片規(guī)格書可以看出,芯片的靜電指標(biāo)越高,系統(tǒng)指標(biāo)不一定更好。

4、從實(shí)際數(shù)據(jù)看芯片靜電和產(chǎn)品靜電的對應(yīng)關(guān)系。

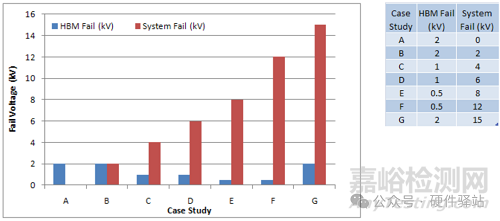

下圖為一官方網(wǎng)站給出了7個(gè)案例的芯片靜電和系統(tǒng)靜電對應(yīng)的關(guān)系,可以看出兩者沒有關(guān)聯(lián)性。

下圖為JEP155B文檔給出的不同HBM指標(biāo)的產(chǎn)品返修率,可以看出,并不是HBM最高為2KV的產(chǎn)品返修率最低。

5、為什么芯片HBM指標(biāo)越高,產(chǎn)品靜電并不一定更好。

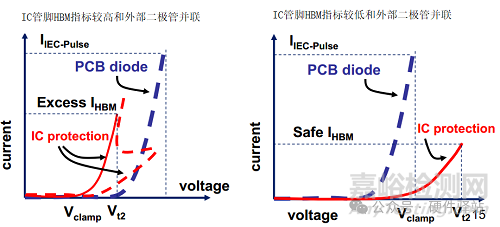

參考下圖:

左圖為HBM指標(biāo)較高的芯片管腳和外部靜電二極管并聯(lián),此片內(nèi)保護(hù)的電路的鉗位電壓更低,動(dòng)態(tài)電阻更小(二極管上升斜率更陡)。

對比右圖可以看出,在芯片片外和片內(nèi)的聯(lián)合靜電保護(hù)設(shè)計(jì)中,左邊的設(shè)計(jì)更容易把靜電引入芯片內(nèi)部,導(dǎo)致片類保護(hù)電路電流過大而超出電流限值,片外的靜電二極管的保護(hù)作用發(fā)揮不出來。

而右圖的HBM指標(biāo)更低的芯片,ESD能量基本都被片外靜電二極管所消耗,從而起到了保護(hù)芯片的作用。

總結(jié):

芯片的靜電指標(biāo)HBM設(shè)計(jì)為最低500V,CDM最低250V,就可以滿足在受控的靜電生產(chǎn)環(huán)境不被損壞。

通過多種數(shù)據(jù)表明,并不是芯片靜電越高,產(chǎn)品的抗靜電指標(biāo)就越好;開發(fā)者需要評估提升芯片靜電指標(biāo)增加的成本是否合理。

如果系統(tǒng)靜電是按A類標(biāo)準(zhǔn)而不是B類標(biāo)準(zhǔn)要求,比如,打靜電時(shí)不能復(fù)位,而芯片靜電設(shè)計(jì)的HBM和CDM指標(biāo)是體現(xiàn)不了此項(xiàng)設(shè)計(jì)的預(yù)期指標(biāo)的。當(dāng)然,系統(tǒng)復(fù)位也和芯片的外圍電路設(shè)計(jì)息息相關(guān),僅根據(jù)芯片的指標(biāo)也不能完全決定系統(tǒng)的指標(biāo)。

來源:硬件驛站