您當前的位置:檢測資訊 > 科研開發(fā)

嘉峪檢測網(wǎng) 2021-11-17 13:13

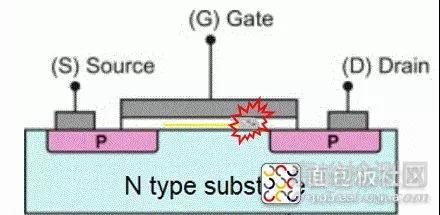

當今各種集成電路微電子器件(CPU,F(xiàn)lash、Memory、controller、Power等),都由大量的各種晶體管與電容、電阻、電感原件構(gòu)成。隨著集成電路器件的搞成集成、高速發(fā)展趨勢,致使集成電路器件(die及die的半成品、Chip)在生產(chǎn)制造(wafer Fab,封裝,測試)與使用(SMT為主)階段對于受到靜電的作用影響越發(fā)敏感。其中的絕緣介電質(zhì)膜層(Gate oxide,passivation等)是靜電損壞的主要結(jié)構(gòu),靜電導致集成電路器件功能損壞的直接原因表現(xiàn)為絕緣膜層的漏電路過大。

圖1:靜電導致晶體管Gate oxide膜層的擊穿失效表征-漏電流過大

圖2:集成電路制造后段wafer sawing工序的rinsing過程的靜電導致絕緣膜層punch through的損壞情形

集成電路微電子器件制造中靜電產(chǎn)生,主要來自取各制程設備操作與生產(chǎn)工序的相關過程,主要表現(xiàn)在:

1.物體間的接觸-分離靜電起電,如wafer在各種制程設備中wafer在ESC(Electro-Static Chuck)上的loading與lift up操作,又如PR(Photo Resist)coating過程中wafer的靜電累積,再如wafer在spin drying過程中的靜電起電與累積等;

2.真空制程設備中的RF plasma作用使wafer膜層上累積靜電,CVD,PVD,DET;

3.高壓rinsing過程wafer上的靜電帶電與靜電累積等;

4.封裝階段wafer切割blue tape的貼膜與撕膜過程的靜電在wafer上的產(chǎn)生與累積。

5.其他制程設備中的靜電產(chǎn)生情形。

圖3:wafer在ESC上的靜電起電情形

圖4:wafer在高壓rinsing過程中的靜電帶電情形

靜電導致集成電路微電子器件發(fā)生功能不良(功能失效及電氣可靠性下降),主要表現(xiàn)為wafer上方的靜電累積過高導致絕緣膜層電性損壞(集中于wafer Fab階段的制程設備與生產(chǎn)工序中),與靜電放電(Electro-Static Discharge,ESD)過程產(chǎn)生的快速電流脈沖stress絕緣介質(zhì)膜層引發(fā)擊穿失效(主要發(fā)生于wafer的probing test,封裝測試階段的die bond、wire bond及各種電性測試工序)。

圖5:wafer上方的靜電累積導致die電性不良的情形

圖6:Wafer/IC高靜電帶電后在電性測試工序發(fā)生ESD的電氣失效情形

來源:Internet