您當前的位置:檢測資訊 > 科研開發

嘉峪檢測網 2025-08-07 22:45

Die Attach,也稱為晶粒粘接(Die Bonding)或晶粒安裝(Die Mount),是半導體行業中一種關鍵工藝。它通過專用設備將硅芯片固定在半導體封裝的支撐結構上,如引線框架(Lead frame)或金屬殼體底座(Metal Can Header)的晶粒焊盤(Die Pad)上。作為半導體后端制造流程的重要環節,Die Attach工藝不僅確保芯片與封裝結構之間的機械穩固連接,還對生產效率和產品質量起著決定性作用。

本文將全面探討Die Attach的基礎知識、其重要性、所使用的材料與方法、工藝參數控制,以及質量與可靠性保障技術。

#01 什么是die attach

Die Attach(晶粒粘接)是半導體器件制造與封裝過程中至關重要的一道工藝環節。它的核心任務是將半導體芯片——

即整個器件的 “智能中樞” ——牢固地粘接到基板或封裝體上。根據電子器件的不同設計和功能需求,封裝形式多種多樣,包括但不限于引線框架(Lead Frame)、陶瓷基板(Ceramic Substrate)以及印刷電路板(PCB)等。

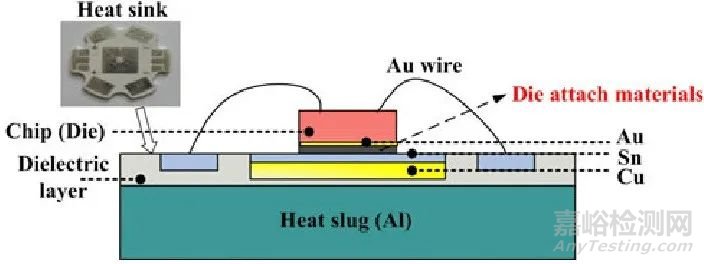

Die Attach工藝對電子設備的整體性能和長期可靠性起著決定性作用。首先,它通過在芯片與封裝體之間形成穩定且堅固的機械連接,有效保護芯片免受組裝、運輸及使用過程中產生的機械沖擊和壓力損傷。其次,粘接層不僅起到機械固定的作用,更是芯片熱管理體系中的關鍵組成部分。它充當高效的熱傳導橋梁,將芯片在運行時產生的熱量迅速傳遞至封裝體或基板,有助于維持芯片的工作溫度在安全且穩定的范圍內,避免過熱帶來的性能退化和壽命縮短。

尤其對于高功率半導體器件而言,Die Attach的熱管理功能尤為關鍵。隨著器件功率密度的不斷提升,芯片產生的熱量顯著增加,合理的熱量散發成為保障器件穩定運行和防止失效的關鍵因素。因此,高品質的Die Attach工藝不僅提升了器件的熱性能,也顯著增強了其機械強度和電氣性能,為現代高性能半導體器件的可靠性和長壽命提供了堅實保障。

1.1 Die Attach的基本作用

在微電子領域,“die”指的是構建了完整電路功能的微小半導體材料片。通常,這些芯片由硅(Silicon)制造,但根據具體應用需求,也可能采用其他半導體材料,如砷化鎵(GaAs)或碳化硅(SiC)。芯片內部集成了晶體管、電容、電阻等多種電子器件,是實現各種電子功能的核心基礎。

1. Die Attach(晶粒粘接)工藝的核心任務

Die Attach工藝的主要目的是將芯片牢固地粘接到封裝體或基板上,實現可靠的機械固定和熱傳導功能。其連接具有兩個關鍵作用:

機械連接

該連接為芯片提供結構上的支撐與固定,使其能夠承受封裝后續工藝、運輸及最終使用過程中產生的機械應力和沖擊,防止芯片移位、破裂或脫層。

熱通道

Die Attach層作為芯片與封裝或基板之間的重要熱橋梁,有效將芯片工作時產生的熱量傳導出去,促進散熱,確保芯片工作溫度保持在安全范圍內。對于功率密度較高的器件,這一點尤為關鍵,因為溫度過高不僅影響性能,還可能導致器件失效。

2. Die Attach對電子器件性能與可靠性的決定性影響

熱管理功能

芯片在工作過程中會產生大量熱能。若不能及時散熱,芯片溫度將持續上升,導致電路性能下降、加速老化甚至發生失效。Die Attach層的熱導性能直接影響熱量傳導效率。例如,金硅(AuSi)共晶合金的熱導率約為57 W/mK,能高效傳遞芯片熱量,保障設備的穩定運行。

機械穩定性保障

半導體芯片材質脆弱,易受機械沖擊和熱循環應力的影響而破裂或出現層間剝離。優質的Die Attach工藝通過形成強勁且均勻的機械結合,提升芯片的抗沖擊能力,降低因熱脹冷縮產生的應力集中,延長器件壽命。

可靠性與缺陷控制

Die Attach層中的缺陷,如空洞(voids)、裂紋或材料不均勻分布,可能引發局部熱熱點或機械應力集中,增加器件故障風險。研究顯示,控制環氧類粘接材料中的空洞率低于1%,能顯著提升功率半導體器件的長期可靠性和使用壽命。

綜上所述,Die Attach不僅是實現芯片與封裝的物理連接,更是確保器件熱管理、機械穩固及整體可靠性的重要基礎工藝。隨著半導體技術向高性能、高功率密度方向發展,Die Attach工藝的質量和材料選擇對提升終端電子產品的性能和壽命起到越來越關鍵的作用。

1.2 Die Attach 使用的材料

用于Die Attach的材料統稱為晶粒粘接材料(Die Attach Materials,簡稱DAMs),主要包括釬焊合金、導電膠以及共晶合金等。材料的選擇不僅關系到機械強度,還需綜合考慮其熱導率、電導率以及與芯片和基板的材料兼容性,因而對最終電子器件的性能和壽命具有決定性影響。

根據材料屬性和應用需求,Die Attach材料大致可分為三大類:金屬合金、陶瓷材料和聚合物材料,各具優勢和局限,適用于不同的應用場景。

1. 金屬合金類

金屬合金材料以其優異的熱導和電導性能,廣泛應用于高性能和高功率半導體器件中。常見的金屬合金包括:

金錫合金(AuSn)

熔點約280°C,熱導率高達約58 W/mK。憑借其優異的熱導性和機械強度,AuSn是高功率器件中理想的Die Attach材料,能有效保證芯片的散熱效率和結構穩定性。但由于金屬材料中金的成本較高,使得整體材料成本相對較大,限制了其在成本敏感型應用中的普及。

金硅合金(AuSi)

典型共晶合金,熔點約363°C,適用于工作溫度較高的環境,且同樣具備良好的熱導性能(約57 W/mK)。其較高的熔點使其更適合高溫工況下的器件封裝,保證長期的熱穩定性。

2. 陶瓷類材料

以銀填充玻璃(Silver-filled Glass)為代表的陶瓷類Die Attach材料,兼具良好的熱性能與電氣絕緣特性。

熱導率:通常在3~4 W/mK范圍,雖然低于金屬合金,但足以滿足大多數普通功率器件的散熱需求。

加工溫度:一般低于200°C,相比金屬合金具有更低的工藝溫度,適合溫度敏感型芯片。

優勢:具備優良的電絕緣性能,適合對電氣隔離要求較高的應用,同時成本相對適中。

3. 聚合物類材料

聚合物Die Attach材料主要以環氧樹脂為基礎,填充銀粒子以提升導熱性能,是目前應用廣泛的低成本方案。

純環氧樹脂的熱導率較低,僅約0.2 W/mK,但通過添加銀粒子填料,熱導率可提升至3~4 W/mK,接近銀填充玻璃陶瓷的水平。

加工溫度:通常低于150°C,工藝相對簡單,兼具較好的機械強度和粘接性。

應用:因成本較低且工藝靈活,廣泛應用于中低功率器件及成本敏感型產品。

不同應用場景下,Die Attach材料的選擇需要綜合考慮以下關鍵因素:

熱性能:確保芯片的熱量能有效散發,防止過熱導致性能衰退或失效。

電性能:部分材料需具備良好的導電性,或者需要電絕緣特性以防短路。

機械強度:保證芯片在后續制造及使用過程中不受機械損傷。

加工溫度:需兼顧封裝工藝的溫度限制,避免對芯片或基板造成熱損傷。

成本控制:根據產品定位平衡性能與制造成本。

綜上所述,選擇合適的Die Attach材料是實現高性能、高可靠性和經濟性的半導體封裝設計的重要保障。

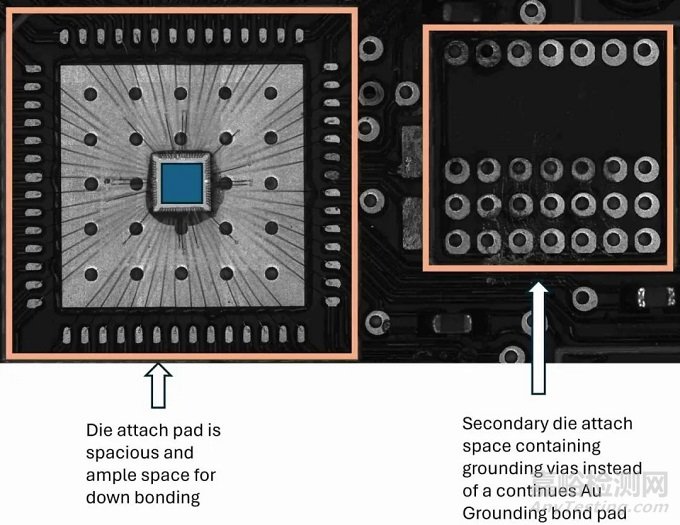

1.3 Die Attach(晶粒粘接)工藝

從晶圓切割下來的芯片(Die)需通過多種不同的Die Attach工藝,精確地固定在基板上的特定焊盤位置,這個焊盤通常稱為“Die Attach Pad”(晶粒粘接焊盤)。基板可以是引線框架(Lead Frame)、金屬底座(Metal Substrate)或其他封裝支撐結構,起到支撐和熱散作用。

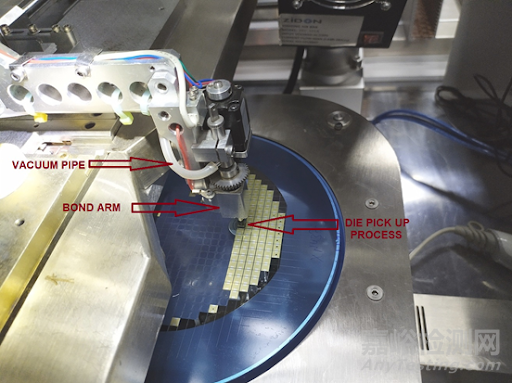

1. Die Attach工藝中的關鍵設備與動作

在Die Attach(晶粒粘接)或Die Bonding(晶粒鍵合)過程中,核心環節是對芯片(Die)與基板(Substrate,通常為引線框架)進行精確對位和粘接。整個過程依賴于高精度的Die Attach設備,主要動作包括:

精密對位:通過視覺系統和運動控制系統,實現芯片與基板焊盤的納米級對準,確保粘接位置準確無誤,避免因偏移導致后續封裝或電氣性能問題。

拾取與放置:使用拾取工具(Pick-Up Tool)或晶粒夾頭(Die Collet)沿Z軸方向下移,輕柔接觸或靠近芯片表面完成拾取與放置動作。

頂出機構配合:設備內設有頂針(Ejector Needles)、針架(Needle Holders)及“胡椒孔盤”(Pepper Pots)等元件,配合拾取系統,實現芯片從晶圓膠膜(Die Attach Film)上的頂出,確保芯片順利脫離并穩定被拾取。

真空固定:拾取過程中,利用真空壓力吸附芯片,防止芯片滑動或脫落,保障芯片在轉移和放置環節的穩定性和準確性。

2. Die Attach工藝流程主要步驟

1)晶圓擴張(Wafer Expansion)

經過測試和探針檢測的晶圓由晶圓制造廠供給。為方便后續自動拾取和粘接操作,晶圓會經過擴張工藝,即增加相鄰芯片間的間距,從而為光學識別(晶圓映射)和機械拾取提供足夠空間。擴張工藝使各芯片保持在晶圓原陣列中的相對位置,但實際占據的面積增加。隨著芯片尺寸日益縮小和厚度減薄,晶圓擴張工藝的應用有所減少,部分生產流程直接采用切割后的單片芯片。

2)Die Attach / Die Bonding

晶粒粘接方式多樣,按材料和工藝性質大致可分為兩類:

共晶粘接(Eutectic Attach)

利用共晶合金(如AuSn、AuSi)通過加熱使材料熔化流動,形成牢固的金屬鍵合,適合高導熱、高可靠性要求的器件。

膠粘接(Adhesive Attach)

主要使用環氧樹脂、紫外固化膠或導電膠等聚合物膠黏劑,在較低溫度條件下固化完成粘接,適合對溫度敏感的器件及成本控制要求較高的應用。

每種方法在材料選擇、加工溫度、壓力控制及粘接性能方面均存在差異,需根據產品設計和工藝要求優化。

#02 常見die attach方式

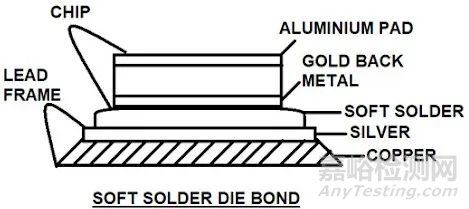

2.1 軟釬焊 Die Attach(Soft Solder Die Attach)

軟釬焊 Die Attach 是一種經典的芯片粘接工藝,采用低熔點金屬釬料作為粘接材料,將芯片牢固地固定在引線框架(Lead Frame)或金屬基板的 Die Pad(粘接焊盤) 上。所使用的釬料通常以線材卷(wire roll)的形式提供,通過設備加工成片狀或預成型(preform)形態用于裝配。

|

分類 |

內容 |

|

優點 |

• 工藝成熟,適合大批量自動化生產。 |

|

• 金屬間連接強度高,導電導熱性能良好。 |

|

|

• 可重復性好,適用于高一致性要求的產品。 |

|

|

局限性 |

• 釬料的熱導率(約30–60 W/m·K)相較共晶合金或銀燒結材料略低。 |

|

• 粘接過程中可能產生空洞(Voids)或焊接不良,影響熱性能與可靠性。 |

|

|

• 某些釬料成分含鉛,需滿足RoHS等環保法規限制。 |

|

|

應用場景 |

• 適用于中等功率要求的功率半導體、LED封裝、傳感器等。 |

|

• 在對成本、工藝溫度控制要求適中的中高端電子封裝中具有廣泛應用。 |

工藝流程概述:

晶圓芯片準備與頂出(Ejection)

芯片(Die)從晶圓切割完成后,仍附著在背膠膜上。通過頂針(Ejector Pin)系統從晶圓背面輕柔頂起,使芯片脫離黏膠,準備進行拾取操作。

芯片拾取與精確貼裝(Pick & Place)

拾取工具(Pick and Place Tool,亦稱 Pick-Up Tool 或 Die Collet)從晶圓上拾取芯片,并在視覺定位系統引導下,將芯片精準放置到引線框架的 Die Attach 區域上。

釬料沉積與貼裝

粘接區域預先鋪放釬料片(Solder Preform)或沉積釬膏(Solder Paste),芯片放置后通過貼裝頭加壓,使其與釬料良好接觸。

加熱回流(Reflow Soldering)

整個結構被加熱至釬料的熔點以上(如 SnPb 合金約183°C,SAC合金約217°C),釬料熔化后潤濕芯片背面與基板金屬面,冷卻后形成穩定的金屬鍵合。

釬料材料特點(常見種類):

SnPb(錫鉛)合金:傳統釬料,潤濕性好,易加工,但不符合RoHS環保要求;

SnAgCu(SAC)合金:無鉛環保釬料,力學性能優良,應用廣泛;

InSn(銦錫)合金:低熔點、高延展性,適用于熱敏器件。

2.2 共晶 Die Attach(Eutectic Die-Attach)

共晶 Die Attach 是一種利用金屬共晶合金(如金-硅、金-錫)作為粘接材料的高可靠性粘接工藝。與軟釬焊方式不同,此工藝不使用預制的釬料片(Soft Solder Preforms),而是依賴芯片與基板(金屬底座或引線框架)之間的金屬層直接反應形成共晶連接。

|

分類 |

內容 |

|

優點 |

• 形成可靠的金屬間結合,具有極高的粘接強度和長期熱穩定性 |

|

• 出色的導熱性(如 Au-Si 熱導率約 57 W/m·K),適用于高功率散熱要求 |

|

|

• 耐高溫、耐老化,適合苛刻環境下的長期使用 |

|

|

• 工藝成熟,易于集成到高端自動化封裝流程中 |

|

|

局限性 |

• 工藝溫度較高(一般 > 360°C),對芯片和封裝材料的耐熱性提出更高要求 |

|

• 對工藝參數(溫度、時間、壓力)控制要求嚴苛,稍有偏差可能導致連接不良或金屬脆化 |

|

|

• 材料成本較高(例如金屬鍍層或AuSn合金) |

|

|

• 不適用于熱敏感器件或低溫工藝平臺 |

|

|

典型應用場景 |

• 射頻(RF)功率器件、高頻通信芯片(如PA、LNA等) |

|

• 激光器、光電探測器等光電器件封裝 |

|

|

• 高可靠性要求的航空航天或軍工電子產品 |

|

|

• 高功率LED、微波模塊、雷達發射端器件等 |

在實際應用中,引線框架的 Die Attach 區域通常只在局部鍍銀(Ag),而芯片背面則鍍有金(Au)層。當芯片被放置在 Die Pad 上后,整個組件會在 Die Attach 設備中加熱至合金的共晶溫度以上(如金-硅共晶溫度約為363°C),觸發金與硅之間的合金反應,熔融并形成牢固的金屬間結合。

為提高界面潤濕性并排除微小氣泡,工藝中還常引入微幅“擦拭運動(Scrub Motion)”,該運動有助于:

加速金屬間原子擴散;

排除粘接區域內的氣泡或污染物;

促進共晶材料在界面均勻鋪展;

提升粘接均勻性和熱導路徑穩定性。

金-硅共晶連接(Au-Si)特別適用于高溫、高功率電子封裝,如雷達、光電器件和射頻功率器件等場景,因其具備:

高熔點(>360°C);

良好的導熱性(熱導率~57 W/m·K);

卓越的可靠性和長期熱穩定性。

2.3 環氧 Die Attach(Epoxy Die-Attach)

環氧 Die Attach 是一種通過環氧類導電或非導電膠粘劑將芯片固定至封裝結構(如引線框架、金屬基板、陶瓷載體等)上的粘接工藝,廣泛應用于中低功率器件的封裝中。

在此工藝中,使用環氧 Die Bonder 或精密點膠設備,先將環氧粘接材料(Epoxy Adhesive)精確滴布在目標基板的粘接焊盤(Die Bond Pad)上。然后通過拾取工具(Pick-Up Tool)將芯片準確放置在膠點上。在貼裝完成后,組件需按照材料廠商推薦的固化曲線(Cure Profile)進行加熱,以使環氧材料交聯固化,形成可靠的機械與熱連接。

|

分類 |

內容 |

|

優點 |

• 工藝溫和,固化溫度低(一般 < 175°C),適用于溫度敏感芯片及器件; |

|

• 粘接過程無需復雜真空或惰性氣氛環境,工藝設備簡單、成本低; |

|

|

• 可通過填充銀粉等方式提升熱導率,導熱性可達 3~8 W/m·K; |

|

|

• 可大面積覆蓋芯片底部,適配尺寸較大或不規則的 Die; |

|

|

• 適合自動化點膠/貼片工藝,重復性與良率較高。 |

|

|

局限性 |

• 相較金屬焊料或燒結銀材料,熱導率和電導率仍偏低(銀填料環氧為中等水平); |

|

• 環氧老化后可能出現脆化或界面脫層,長期可靠性需控制濕氣、熱應力等因素; |

|

|

• 粘接層中可能產生空洞或氣泡,影響熱管理與粘接強度; |

|

|

• 若溢膠至焊盤區域,可能影響后續引線鍵合或封裝步驟。 |

|

|

典型應用場景 |

• 中低功率器件(如邏輯芯片、LED、小信號放大器等); |

|

• 高性價比消費類電子產品(如攝像頭模組、功放模組等); |

|

|

• 環境條件要求溫和、無需極高導熱或電導性能的場合; |

|

|

• 對封裝尺寸、粘接面積有較高靈活性要求的產品,如大面積芯片、電源模塊。 |

常用環氧類材料包括:

環氧樹脂(Epoxy): 應用最廣,通常需加熱固化,具備良好機械性能和較低加工溫度;

聚酰胺(Polyimide): 適用于高溫環境,耐熱性能更優;

填銀環氧(Ag-filled Epoxy): 在環氧基體中加入高導熱銀顆粒,提升熱導率至 3–8 W/m·K,兼顧粘接強度與熱管理能力;

銀粉玻璃材料(Glass-Frit with Ag): 屬于復合材料,可提供更強的耐溫性和低揮發性,適用于特殊封裝需求。

芯片貼裝后,其四周與環氧粘接劑接觸形成的區域即為“環氧覆蓋區(Epoxy Coverage Area)”,該區域的大小與均勻性直接影響芯片的散熱通道和應力分布。覆蓋不充分可能導致空洞或應力集中,而覆蓋過多則易產生溢膠,污染焊盤或引腳區,影響后續封裝質量。

工藝特點:

固化溫度低(一般在 125~175°C 之間),適合溫度敏感型芯片;

工藝靈活,便于實現自動化與批量生產;

材料配方多樣,可根據需求選擇導熱性、粘接強度、低釋氣性等性能。

2.4 紫外固化 Die Attach(UV Die Attach)

紫外固化 Die Attach 是一種利用紫外光照射促使粘接材料發生交聯反應,從而實現芯片固定的工藝方法,常用于處理丙烯酸類壓敏膠(PSA)或紫外光敏型 Die Attach Film(DAF)。

該工藝通過紫外線(通常波長范圍為 365~400 nm)照射粘接膜,使其粘性降低、力學強度上升,形成更加穩定且可控的粘接界面。特別適用于薄型晶圓、堆疊封裝或芯片對膜類結構的應用。

技術優勢:

|

類型 |

描述 |

|

粘接力精準可控 |

UV固化可調整粘接層的剪切強度和表面黏附性,減少芯片飛脫、移位等風險。 |

|

適用于超薄晶圓 |

在堆疊封裝(如PoP、3D封裝)中,可有效提升對薄晶圓的控制力,防止切割過程中芯片飛出。 |

|

工藝兼容性強 |

紫外固化膜廣泛兼容當前主流的晶圓貼片、切割與鍵合工藝,支持大尺寸晶圓。 |

|

無熱固化影響 |

不依賴熱源,對溫度敏感器件尤其友好。 |

關鍵應用挑戰與注意事項:

固化深度受限:UV固化存在光穿透限制,尤其在多層膜或厚封裝中,需特別設計UV光強與照射時間;

需編程式光照曲線:為了確保固化均勻性和防止邊緣未固化,UV照射常需設置逐步增減的強度輪廓;

需防止膠絲與溢膠問題:UV不充分固化時可能出現“adhesive whiskering”(膠絲)或膠水遷移,應適配清潔室與防污染要求;

工藝參數需匹配材料特性:不同 DAF 材料的UV響應性能差異顯著,需通過實驗驗證照射時間、波長、強度等。

典型應用場景:

|

應用方向 |

說明 |

|

堆疊封裝(Stacked Die / 3D封裝) |

如 eMMC、PoP、CIS模組中,UV DAF 可實現芯片間粘接與精準定位控制。 |

|

超薄晶圓切割 |

有效提升切割精度,避免薄片飛脫或粘連。 |

|

CMOS圖像傳感器(CIS)封裝 |

在影像模組中,DAF 加 UV 固化可兼顧透明性、潔凈度與高可靠性。 |

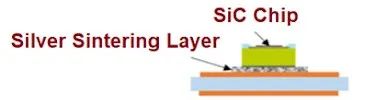

2.5 銀燒結 Die Attach(Silver Sintering Die Attach)

銀燒結是一種高可靠性、無鉛環保的新型晶粒粘接工藝,通過納米級或微米級銀顆粒在一定溫度、壓力與時間條件下燒結成致密導熱層,用于取代傳統軟釬焊或共晶粘接。

銀燒結技術被廣泛認為是高功率、高溫、高可靠性封裝領域的重要趨勢,尤其適用于功率器件、汽車電子、射頻模塊、SiC/GaN等寬禁帶半導體器件的封裝。

技術優勢:

|

類別 |

描述 |

|

高熱導率 |

燒結銀層的熱導率可達 200~250 W/m·K,遠高于傳統釬料(如SnAgCu約60 W/m·K)與填銀環氧樹脂。 |

|

高熔點、高溫可靠性 |

燒結銀本身熔點高達 962°C,工作溫度范圍寬,不易發生蠕變或再熔問題,適合 >250°C 工作環境。 |

|

優異的機械強度與抗疲勞性能 |

燒結層具有高度致密的金屬連接結構,具備良好的剪切強度與抗熱疲勞特性,可顯著提升焊點壽命。 |

|

無鉛環保 |

不含有害重金屬,符合RoHS等環保法規要求。 |

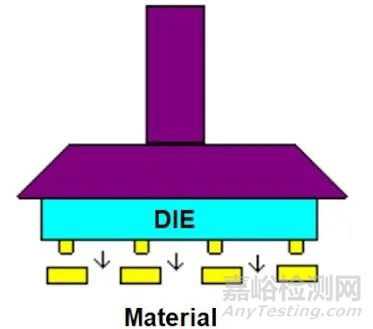

工藝流程概述:

|

工藝步驟 |

說明 |

|

1. 銀漿印刷或點膠 |

將銀燒結膏(Silver Paste)印刷至基板粘接區,常使用絲網印刷、模板點膠或噴印方式。 |

|

2. 芯片貼裝 |

將晶粒(Die)準確定位至銀漿上,保證良好覆蓋與對準。 |

|

3. 燒結固化 |

在 200~300°C 下進行數分鐘至數十分鐘燒結處理,部分系統需施加壓力(常為 10~50 MPa),促使銀顆粒致密化并形成金屬鍵合。 |

工藝挑戰:

|

問題 |

說明 |

|

燒結溫壓耦合敏感 |

粘接強度與可靠性高度依賴燒結溫度、壓力和時間參數,需精準控制與材料匹配。 |

|

成本較高 |

銀燒結膏價格昂貴,設備投入成本高,適合高附加值產品使用。 |

|

對基板平整度和芯片翹曲敏感 |

燒結層為剛性連接,需控制芯片翹曲與粘接面的共面性,避免虛焊或翹邊失效。 |

典型應用場景:

|

應用 |

說明 |

|

SiC/GaN 等寬禁帶半導體器件 |

在高溫、高頻、高壓下穩定工作,傳統釬焊難以滿足其可靠性需求。 |

|

汽車功率模塊(如IGBT) |

適用于主驅逆變器、OBC、DC-DC等高功率模塊封裝。 |

|

工業與航天高可靠性器件 |

如高可靠電源模塊、雷達、衛星通信等對熱穩定性要求極高場合。 |

2.6 熱壓Die Bonding(Thermocompression Die Bonding)

熱壓Die Bonding,又稱為熱壓接合或擴散鍵合(Diffusion Bonding),是一種通過同時施加熱能和機械壓力,使芯片與基板或引線框架等金屬接觸面之間發生原子級結合的精密粘接工藝。

其核心原理是:在較高溫度(通常為200°C至450°C)和一定壓強(例如數兆帕)條件下,使兩種金屬材料的接觸面發生原子間擴散。隨著時間的延長,原子在接觸面處互相滲透,逐步形成牢固的冶金結合層(Metallurgical Bond),實現無中介材料(如焊料、膠水)的直接鍵合。

工藝流程:

|

步驟 |

說明 |

|

1. 表面預處理 |

對芯片與基板的金屬表面進行清洗、等離子活化或濺射處理,以去除氧化層并提高擴散活性。 |

|

2. 芯片貼裝 |

使用熱壓Die Bonder將芯片準確對位并置于金屬焊盤上。 |

|

3. 熱壓過程 |

在惰性氣氛或真空下,同時施加高溫(通常為 250–450°C)和高壓(通常為 10–100 MPa),維持幾秒至幾分鐘,促成金屬擴散鍵合。 |

|

4. 冷卻與釋放 |

保持壓力條件下逐步冷卻,使金屬鍵合層定型,形成穩定結合界面。 |

優勢特性:

|

類型 |

優勢說明 |

|

無中間材料 |

不依賴焊料或粘接劑,避免引入額外界面或雜質,提高熱穩定性。 |

|

極高可靠性 |

冶金鍵合為最牢固的界面形式之一,具備超強耐熱、抗老化、抗熱循環能力。 |

|

優異的熱導性能 |

鍵合界面幾乎無空洞、無中斷,熱阻極低,適用于高功率密度器件。 |

|

環保無鉛 |

無需焊料,符合環保法規,適合綠色制造。 |

工藝挑戰:

|

項目 |

描述 |

|

設備與成本較高 |

熱壓設備成本高,對溫度、壓力、時間精度要求嚴格,適合中高端制造線。 |

|

對表面清潔度要求高 |

表面必須無氧化層或有機污染,否則會阻礙原子擴散。需使用高潔凈制程或等離子處理。 |

|

芯片翹曲與應力敏感 |

熱壓過程可能引發芯片變形或微裂紋,尤其對薄片或脆性材料需優化參數。 |

典型應用場景:

|

應用領域 |

說明 |

|

MEMS器件封裝 |

對鍵合密封性和可靠性要求極高,熱壓工藝可實現高真空密封。 |

|

高功率射頻模塊 |

射頻功放芯片(如GaN、GaAs)對導熱性能和機械穩定性要求高。 |

|

軍工、航天電子器件 |

要求極高的環境適應性與長期可靠性。 |

|

先進3D封裝(如TSV堆疊) |

適合用于硅互聯、晶圓堆疊等先進封裝結構中,實現芯片間直接鍵合。 |

2.7 倒裝芯片 Die Attach(Flip Chip Die Attach)

倒裝芯片粘接(Flip Chip Die Attach)是一種先進的芯片互連方式,其顯著特點是將芯片“翻轉”安裝,使其有源面(Active Surface)朝下,通過預先形成的焊球(Solder Bumps)或導電凸點直接與基板上的金屬焊盤連接,形成電氣與機械一體化連接。

該工藝不再依賴傳統的金線鍵合(Wire Bonding),大大縮短互連路徑、提升信號完整性,廣泛用于高性能計算、移動通信、汽車電子、MEMS等領域。

Flip Chip Die Attach 工藝結構與關鍵功能區

整個倒裝芯片粘接過程可細分為三個關鍵功能結構:

|

區域 |

說明 |

|

1. 凸點下金屬化(Under Bump Metallization, UBM) |

UBM 是焊球與芯片內部金屬互連(通常為 Al 或 Cu)之間的界面金屬疊層結構,起到橋接、電氣兼容、阻擋擴散及改善潤濕性的作用。典型UBM結構包括: |

|

• 粘附層(如 Ti/TiW) |

|

|

• 阻擋層(如 Ni) |

|

|

• 潤濕層(如 Cu) |

|

|

• 抗氧化層(如 Au) |

|

|

2. 芯片凸點與粘接材料(IC Bump and Bond Material) |

凸點可通過多種方法形成: |

|

• 蒸發沉積(Evaporation) |

|

|

• 電鍍(Electroplating) |

|

|

• 模板印刷(Stencil Printing) |

|

|

• 噴焊(Jetting) |

|

|

常用焊料包括 SnAgCu、SnPb、SnAg 或導電聚合物(如ACF/ACP)。材料與凸點形狀需精準控制,以確保后續對準和焊接的一致性。 |

|

|

3. 基板金屬化(Substrate Metallization) |

基板通常為BT樹脂或有機層壓板(如FR-4、ABF),表面需預處理并形成金屬焊盤,典型結構為: |

|

• 銅焊盤 + 表面處理層(OSP、ENIG、ENEPIG等) |

|

|

• 焊膏或助焊劑印刷后,進行芯片貼裝與回流焊。為兼容其他元器件組裝(如SMD),焊料類型選擇需注意熔點匹配。 |

Flip Chip Die Attach 工藝流程:

|

步驟 |

描述 |

|

1. 凸點形成 |

在芯片焊盤上形成凸點(通常為焊球或金屬柱),并進行UBM處理。 |

|

2. 芯片翻轉與對準 |

使用Flip Chip Die Bonder將芯片翻轉,使凸點朝下,并精確對準基板焊盤。 |

|

3. 貼裝與壓接 |

芯片貼至基板后,施加適當壓力以確保凸點與基板充分接觸。 |

|

4. 回流焊或固化 |

將組裝好的芯片與基板加熱至焊料熔點,使凸點熔化后形成焊接連接。導電膠或熱壓材料可用于低溫互連場合。 |

|

5. Underfill填充 |

回流后在芯片周邊填充環氧型Underfill材料,增強機械強度并防止焊點疲勞失效。 |

優勢特點:

|

類型 |

描述 |

|

高性能互連 |

減小互連長度,顯著降低寄生電感與電容,提升信號速率與傳輸完整性。 |

|

優異散熱能力 |

芯片底部可直接接觸基板或通過金屬凸點散熱,支持高功率應用。 |

|

高集成度 |

支持多芯片集成(SiP)、2.5D/3D封裝,適用于小型化設計。 |

|

可靠性更高 |

配合Underfill材料可有效緩沖熱應力,增強抗震耐熱能力。 |

工藝挑戰:

|

類型 |

描述 |

|

貼裝精度要求高 |

對準公差一般需控制在 ±10 µm 以內。 |

|

熱應力管理難度大 |

芯片與基板材料CTE不匹配易引起焊點疲勞,應結合Underfill優化結構。 |

|

設備成本較高 |

Flip Chip Bonder、再流爐、Underfill點膠等設備投資較大。 |

典型應用場景:

|

應用領域 |

說明 |

|

高端CPU/GPU |

如英特爾、AMD等的高性能芯片互連方案。 |

|

RF前端模組 |

包括功率放大器(PA)、低噪聲放大器(LNA)等對小型化與性能要求極高的產品。 |

|

汽車電子 |

功率芯片、高速通信芯片等需高可靠性與熱管理能力的場景。 |

|

移動終端與可穿戴設備 |

對封裝厚度、性能密度要求高的智能手機、智能手表等。 |

以下是對七種常見Die Attach(晶粒粘接)工藝的總結

|

工藝名稱 |

粘接原理 |

典型材料 |

優點 |

局限性 |

典型應用 |

|

軟釬焊 Die Attach (Soft Solder)

|

通過熔融軟釬料(金屬絲/焊膏)將芯片焊接到引線框架或基板上 |

SnPb、SnAgCu |

• 工藝成熟,適合自動化 |

• 易產生空洞,影響可靠性 |

中功率半導體、LED、傳感器等 |

|

• 連接強度高 |

• 含鉛釬料環保限制 |

||||

|

• 導熱導電性好 |

• 熱導率略低于共晶 |

||||

|

共晶 Die Attach (Eutectic)

|

在金屬界面形成共晶合金(如Au-Sn或Au-Si)連接,粘接牢固 |

AuSn、AuSi |

• 高溫穩定性好 |

• 金屬成本高 |

高頻/高功率器件、雷達、射頻器件 |

|

• 導熱導電性能優異 |

• 工藝需控溫精確 |

||||

|

• 重復性好,可靠性高 |

|

||||

|

環氧 Die Attach (Epoxy)

|

利用環氧類導電膠水粘接芯片,后續加熱固化 |

填銀環氧、聚酰亞胺 |

• 工藝簡單,低溫固化 |

• 熱導率較低(3~4 W/mK) |

消費類電子、傳感器、低功率芯片 |

|

• 成本低 |

• 易受濕氣老化影響 |

||||

|

• 可兼容多種封裝結構 |

|

||||

|

紫外固化 Die Attach (UV Adhesive)

|

利用紫外線照射使壓敏膠快速固化,形成臨時或永久連接 |

丙烯酸類 PSA 膠膜 |

• 固化快速 |

• 紫外線穿透性要求高 |

堆疊芯片封裝、移動設備薄芯片應用 |

|

• 低溫、低應力 |

• 固化后熱穩定性較弱 |

||||

|

• 適用于薄晶圓、堆疊芯片 |

|

||||

|

銀燒結 Die Attach (Ag Sintering)

|

在加熱和加壓下,銀納米顆粒發生燒結,形成高強度粘接層 |

納米銀漿 |

• 極高熱導率(>150 W/mK) |

• 設備和材料成本高 |

電動汽車IGBT模塊、功率半導體、航天 |

|

• 高熔點,抗蠕變 |

• 工藝窗口要求嚴格 |

||||

|

• 適用于高溫高功率場景 |

|

||||

|

熱壓 Die Attach (Thermocompression)

|

在高溫高壓下金屬原子間擴散鍵合,無需焊料或膠水 |

金屬-金屬擴散對(如Au-Au) |

• 無污染、無助焊劑殘留 |

• 工藝復雜 |

高可靠性軍工、氣密封裝、MEMS |

|

• 高可靠性 |

• 對金屬純度與表面處理要求高 |

||||

|

• 適合真空、氣密封裝 |

|

||||

|

倒裝芯片 Die Attach (Flip Chip)

|

芯片翻轉,使用焊球/導電凸點與基板焊盤直接連接 |

焊球(SnAgCu)、ACF/ACP |

• 互連距離短,電性能優 |

• 設備成本高 |

高端CPU/GPU、5G射頻芯片、汽車電子 |

|

• 散熱路徑短,熱性能佳 |

• 需精密對位與可靠Underfill工藝 |

||||

|

• 支持高集成密度封裝 |

|

#03 Die Attach的質量與可靠性

Die Attach的質量和可靠性是半導體器件性能穩定性和使用壽命的關鍵保障。高品質的粘接不僅優化芯片的熱管理效率,還能顯著提升結構強度和電氣連接的穩定性,因此必須在制造全過程中嚴格評估和控制。

3.1 粘接質量評估技術

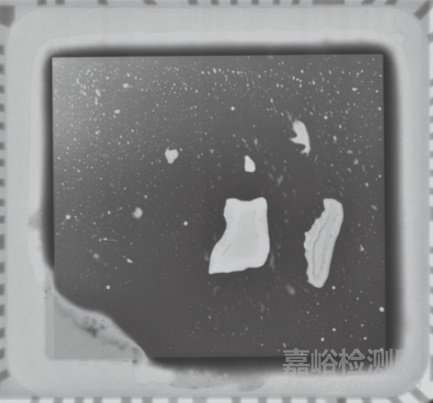

為確保Die Attach的高質量,業界廣泛采用多種無損檢測技術來識別和量化潛在缺陷:

X射線成像(X-ray Imaging)

通過X射線穿透封裝層,生成內部結構圖像,能夠有效檢測粘接層中的空洞、裂紋、脫層等缺陷。空洞區域因吸收X射線較少,在圖像中表現為明顯暗斑。除此之外,X射線成像還能分析粘接膠層的厚度及均勻性,幫助優化工藝參數。

超聲波掃描(Ultrasonic Scanning)

利用高頻聲波探測粘接層內部狀況。超聲波在遇到缺陷(如裂紋、分層)時會產生反射,通過分析回波特征可識別出微小缺陷,尤其是X射線難以探測的局部微裂紋和分層現象。

以上無損檢測方法能夠在早期發現生產缺陷,及時調整工藝參數或篩選不良產品,顯著提升產品良率與可靠性。

3.2 Die Attach常見失效模式

深入理解粘接層的失效機理,有助于改進材料選擇和工藝設計,從根本上提高器件的可靠性:

空洞(Voids)

空洞多因氣體夾帶或水分未及時排出所致,形成的空洞區域阻礙熱流傳導,導致局部芯片過熱。特別在高功率器件中,空洞面積占比超過10%時,芯片結溫顯著升高,壽命和性能大幅下降。空洞還會導致機械應力集中,加速界面疲勞。

脫層(Delamination)

指粘接界面或膠層內部層與層之間發生分離,通常由于不同材料的熱膨脹系數(CTE)差異較大,引發熱循環中的機械應力過載。舉例來說,硅芯片CTE約為2.6 ppm/°C,引線框架CTE約為7 ppm/°C,而環氧粘接材料CTE可高達23 ppm/°C,這種不匹配容易造成界面分離,嚴重時導致電氣性能和散熱功能失效。

開裂(Cracking)

多由熱應力、機械沖擊或長期疲勞引起。裂紋可穿透粘接層,降低熱和電性能,甚至導致芯片斷裂失效。研究表明,僅5微米寬度的微裂紋即可顯著影響整體性能,尤其在高頻和高功率應用中風險更大。

Die Attach質量的優劣直接影響芯片的熱管理效率和機械完整性,進而決定整個半導體器件的性能和壽命。通過先進的無損檢測技術對粘接層缺陷進行早期發現與控制,以及針對常見失效模式的深入理解和預防,半導體制造商能夠大幅提升產品的穩定性和可靠性,滿足日益復雜多變的應用需求。

#03 總 結

Die Attach雖是半導體封裝工藝中的 “幕后英雄” ,卻是芯片性能和可靠性的基石。選擇合適的粘接材料與工藝,不僅保障芯片結構穩定,更確保電子產品安全高效運行。未來,隨著材料科學和制造技術的進步,Die Attach工藝將繼續推動半導體產業向更高峰邁進。

來源:芯片技術與工藝