您當前的位置:檢測資訊 > 科研開發

嘉峪檢測網 2021-04-22 09:34

基于華宏0.35μm BCD工藝,設計了一種可以source(輸出)和sink(吸入)電流的低壓DDR(Double Data Rate)終端調整器芯片。該芯片支持2.5V輸入電壓軌和3.3V輸入電壓軌。該芯片功率電源電壓范圍1.1~3.5V,并且具備低噪聲、低功耗、快速響應的特性,可以滿足DDR、DDR2、DDR3、DDR3L、DDR4 的VTT總線電壓要求。

DDR存儲器中文名稱為“雙倍數據率同步動態隨機存儲器”,是在同步動態隨機存儲器(SDRAM)的基礎上發展而來,與單數據速率相比,DDR技術實現了一個時鐘周期內進行兩次讀/寫操作,即在時鐘的上升沿和下降沿分別執行一次讀/寫操作。由于DDR具有出眾的性能、較低的功耗以及更具競爭力的成本,目前已普遍應用在電腦和手機的內存當中。DDR存儲器不斷更新換代,數據速率逐漸提高,容量逐漸增加,工作電壓逐漸降低,需要更加先進的電源管理系統提供支持。

由于DDR是一種雙向數據傳輸模式的內存,其“雙向數據傳輸”特性要求供電系統提供既可輸出驅動也可吸入電流的能力,因此兼備Sink/Source電流能力的終端調整器成為首選。同時,DDR的輸入電源要以低阻抗連接到穩壓器輸出上,隨著時鐘頻率升高、電源電壓降低以及負載電流增大,為避免總線上負載改變引起該輸入電源電壓變化,需要調整器具有大電流輸出能力和良好的負載瞬態響應性能。

本文介紹了一種可同時用作DDR、DDR2、DDR3、DDR3L、DDR4存儲器總線電壓的低壓終端調整器芯片設計,可以為DDR存儲器提供一套完整的低功耗解決方案。該電路可實現快速瞬態響應,僅僅只需20μF輸出電容。輸入電壓(VIN)支持2.5V和3.3V電源軌,獨立功率電源(VLDOIN)最低達到0.9V,提升電源效率。當輸出電壓建立時,該芯片可以產生一個高阻抗的PGOOD(輸出電壓檢測)信號。可實現輸出穩定總線電壓VTT(0.5V~1.8V),并可以實現source和sink電流3A以上,靜態電流僅800μA。

電路設計與實現

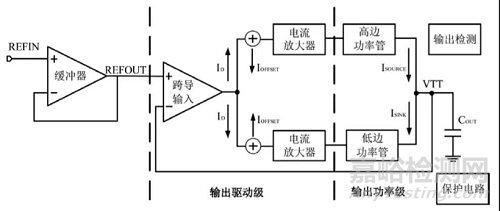

本文設計的DDR終端調架構如圖1所示,主要包含輸入緩沖器、跨導放大器、高低邊電流放大器、高低邊功率管、輸出檢測電路以及過流、過溫、欠壓保護單元。工作原理如下:基準輸入REFIN經過緩沖器單元,產生緩沖參考輸出電壓REFOUT,REFOUT端口也可提供±10mA灌電流/拉電流,REFOUT電壓經過輸出驅動級,驅動高低邊功率管,產生DDR總線電壓VTT,并可以提供source和sink電流,電流值為±3A。

圖1 DDR終端調整器架構圖

圖1中跨導輸入級檢測基準輸出電壓REFOUT和輸出電壓VTT,將兩者的差分電壓轉換成差分電流ID輸出到后級的電流放大器,電流放大器由多級電流鏡構成,通過電流鏡的鏡像與放大后,通過高/邊功率管產生ISINK/ISOURCE輸出調整電流。

由于跨導運放內部節點均為低阻抗節點,整個反饋網絡為單極點系統,主極點位于輸出端,其大小為輸出功率管的跨導與負載電容的比值,除主極點外所有極點均位于高頻,環路單位增益帶寬為GM/COUT,其中GM為電路的跨導,COUT為負載電容,環路的單位增益帶寬可以設計的很高,并且可以根據應用通過外圍負載電容進行調整,保證了瞬態響應能力。

01.緩沖器電路

緩沖器電路如圖2所示,采用折疊低壓cascode輸入級,推挽輸出級,密勒補償結構,可以實現2.375V~3.5V工作電壓下,輸出±10mA電流。緩沖器輸入信號為基準輸入REFIN,通過單位增益的反饋連接輸出緩沖參考輸出電壓REFOUT。由于緩沖器采用了兩級運放結構,增益很高,可以保證REFOUT的電壓精度在±1%以內。

圖2 低壓緩沖器電路

其中R2、Q2和R1、Q1分別為sink/source過流保護電路,當source電流超過過流保護限時,R2上的壓降增大,Q2管開啟,對PM1管的柵極電壓進行鉗位,達到限流效果。同理,sink電流超過過流保護限時,Q1對NM1的柵極電壓進行鉗位,達到限流效果。則緩緩器電路的sink和source電流限流值為:

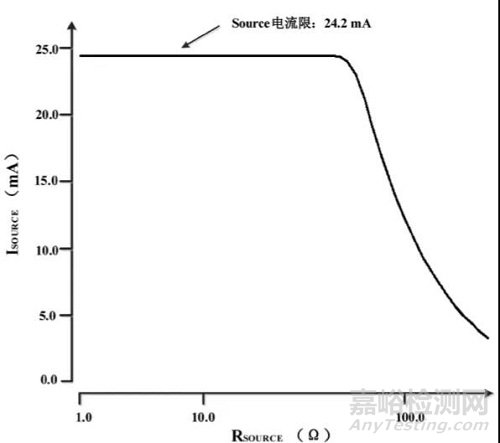

緩沖器電流限sink和source電流限仿真圖如圖3和圖4所示。仿真顯示,sink和source電流限均在24mA左右,滿足系統±10mA要求。

試件應在試驗前、試驗后功能完好且所有參數符合規范要求。應通過持續參數監測和參數測試(小)(即,在室溫和工作電壓條件下試樣無瑕疵功能的關鍵參數測試)進行驗證。

圖3(左) sink電流限仿真圖;圖4(右) source電流限仿真圖

02.輸出誤差放大器電器

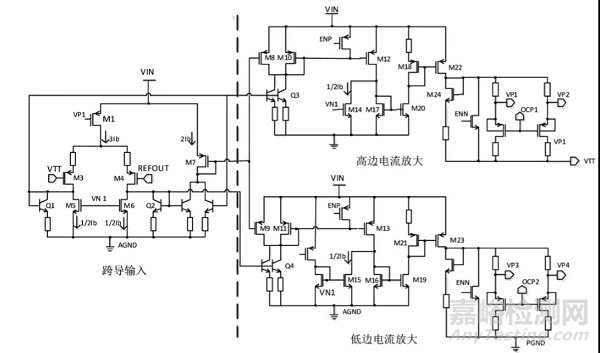

輸出誤差放大器上邊功率管和下邊功率管產生source和sink電流,并穩定環路,產生穩定電壓。主要分為跨導輸入、高邊電流放大和低邊電流放大三部分。如圖5所示。

圖5 輸出誤差放大器線路圖

運放的增益由各個跨導級產生,M1管的偏置電流為3Ib,M3、M4管電流為3/2Ib,M5、M6的偏置電流設定為1/2Ib,則Q1、Q2管的偏置電流為Ib。

當VTT電位低于REFOUT時,Q1管電流為Ib+i,Q2管電流為Ib-i,則Q5、Q6管電流分別為1/2Ib+i和1/2Ib-i,M7管電流為Q1、Q2管鏡像的電流和為2Ib,并鏡像到M8、M9管。Q1管和Q2管電流鏡像到Q3管和Q4管,電流為Ib+2i和Ib-2i。Q3管與M8管的電流差值2i通過M10、M12、M17、M20、M18、M22、M24管組成的電流鏡鏡像到source端功率管輸出對VTT端充電。Q4管與M9管的電流差值-2i,關斷了后面的電流鏡,從而關斷sink功率管。

當VTT電位高于VTTREF時,情況相反,Q1管電流為Ib-i,Q2管電流為Ib+i,M7管電流為Q1、Q2管鏡像的電流和為2Ib,并鏡像到M8、M9管。Q1管和Q2管電流鏡像到Q3管和Q4管,電流為Ib-2i和Ib+2i。Q4管與M9管的電流差值2i通過M11、M13、M16、M19、M21、M23管組成的電流鏡鏡像到sink端功率管輸出對VTT端放電,source功率管關斷。

M14與M15管引入1/2Ib電流以保證當M12管與M13管的電流小于1/2Ib時,source端與sink端功率管全部關斷,防止VTT電位與VTTREF電位接近時source端與sink端功率管同時導通,因此正常工作時VTT與VTTREF之間存在失調電壓,失調電壓的大小為:

其中k為M10管與M12管寬長比,gm3為輸入級M3管的跨導。由于運放由跨導級組成,因此運放內部節點均為低阻抗節點,反饋環路呈單極點系統,主極點位于調整器輸出端。

03.上下邊功率管電路

本文設計上下邊功率管如圖6所示,M40和M41為上邊功率管,可以提供3A source電流。M42和M43為下邊功率管,提供3A sink電流。

圖6 上下邊功率管電路

當M40、M41輸出電流時,受輸出級誤差放大器控制,M42和M43處于關斷狀態。同理,當M42和M43吸入電流時,M40和M41處于關斷狀態。當空載時,由于誤差放大器引入的失調,M40、M41、M42、M43全部關斷。確保功率管共態導通電流為零。

仿真結果與版圖設計

采用華宏0.35μmBCD工藝,設計并實現了一種低壓DDR終端調整器,電源電壓范圍2.375~3.5V、輸出電壓VTT范圍可以提供±3A的source和sink電流以及實現快速響應的功能。

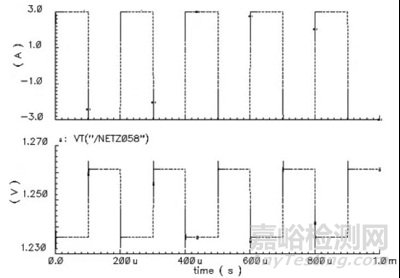

DDR調整器的輸出電流瞬態仿真圖如圖7所示。REFIN電壓為1.25V。因此VTT輸出電壓為1.25V。仿真可以看出,輸出電流±3A,1.25V輸出電壓條件下,輸出容差不超過±20mV,滿足系統±34mV容差要求。并且具備快速響應的能力。

圖7 輸出電壓瞬態仿真圖

表1為不同電源電壓、功率電壓下對應的輸出總線電壓VTT、REFOUT電壓精度以及VTT電流限的仿真結果。以及可以滿足的DDR種類。從仿真結果可以看出,電路在3.3V電壓軌和2.5V電壓軌下,產生總線電壓VTT值、緩沖參考輸出REFOUT精度、sink/source電流限,可以滿足DDR1、DDR2、DDR3、DDR3L、DDR4終端調整器的電壓電流需求。

表1 仿真結果

本文設計的低壓DDR終端調整器芯片版圖如圖9所示。在調整器的版圖設計中,首先要注意功率管電流均勻性,需要多層金屬布線。功率管采用雙環設計,減小閂鎖發生條件。同時基準電源、基準的地線直接連接到電源和地的PAD上,減少其他模塊的干擾。

圖9 低壓DDR終端調整器芯片版圖

結論

本文設計了一種一種可以source和sink電流的低壓DDR終端調整器芯片。隨后詳細給出了DDR終端調整器結構設計、緩沖器電路設計、輸出誤差放大器設計以及上下邊功率管設計的原理圖。本電路采用華宏0.35μm BCD工藝制作。仿真結果表明,在2.5V和3.3V電源軌下,可以實現輸出VTT總線電壓范圍0.6V~1.25V,緩沖參考輸出REFOUT精度在±0.1%, source和sink電流可以達到3A以上,可以滿足DDR1、DDR2、DDR3、DDR3L、DDR4對終端調整器的電壓和電流需求。

來源:環境技術核心期刊