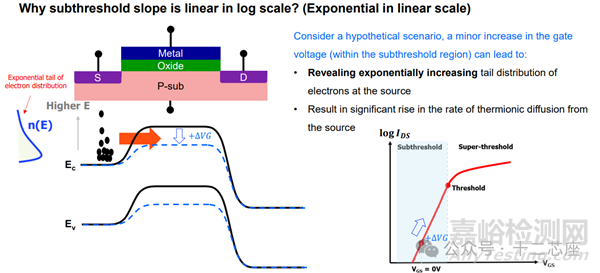

在亞閾值區,若以對數尺度繪制其曲線,會呈現出線性關系,具體遵循自然對數規律(即ln(ex)=x)。這一現象表明,在達到閾值電壓(VT)之前,亞閾值傳導(或漏電流)在自然狀態下呈指數變化。

為什么閾下斜率在對數尺度下是線性的?(線性指數)

門電壓的輕微增加(在閾下區域內)

電子在源極處的指數級增長導致從源極的熱電子擴散速率顯著上升.

Subthreshold Swing (SS)SS:

增加或減少id 10倍 (一個數量級) 所需的柵極電壓, SS由對數IDS與VGS斜率的倒數給出。

那么,SS 有哪些影響因素?

溫度,溫度升高,SS 增大。

柵氧化層電容增大,SS 減小;使用high k介質,減小柵氧化層厚度,都可以使 SS 減小。

Si耗盡層電容減小,SS 減小;使耗盡層寬度增大的因素,例如襯底濃度Na減小,襯底偏置電壓增大,會使 SS 減小。

柵氧化層和襯底硅界面會存在一些界面缺陷,能存放電荷,這些缺陷的增加,相當于疊加了一個電容,會使 SS 增大。

溝道長度較小會使得柵控能力減弱, SS 增大。

柵電壓增大,隨著表面反型增強,柵對channel的控制能力就越弱,SS 增大。

其最小可實現值又是多少?

但一些新型器件,如隧穿器件(TunnelingTransistor)以及負電容器件,可以獲得低于此理論值的亞閾值擺幅。

Subthreshold LeakageLeakage

current mechanism-溝道穿通效應-punch through

在相同的閾值電壓下,與A相比,B在亞閾值斜率(SS)上表現得更差。較小的SS(即更陡峭的斜率)對于將關態泄漏降至最低至關重要。

A 和 B 都具有類似的SS,然而,B在VGS=0V時的漏電是A的十倍。

因此在相同的SS下,為了降低動態功率,縮放其VDD。curve右移,Ioff降低。

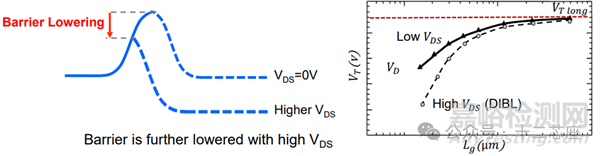

DIBL

Drain Induced Barrier Lowering (DIBL)

知識日記:DIBL, Drain Induced Barrier Lowering, 漏致勢壘降低效應

來自漏極的場強降低了源極處的電子注入勢壘,在柵極長度較短的器件中(在 VDS = 0 時)觀察到的影響更為顯著。

漏極電場向溝道的侵入會降低源端電子注入勢壘,從而導致閾值電壓(VT)下降。該效應受以下因素加劇:

溝道(柵極)長度(Lg)縮短

漏源電壓(VDS)升高

柵極逐漸失去對溝道的控制,而漏極的影響逐漸增強,上述機制還會使關態漏電流(Ioff)上升,并使亞閾值斜率(SS)惡化。

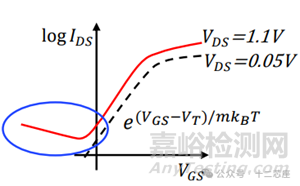

漏極感應勢壘降低(DIBL)會在漏源電壓 VDS 升高時使閾值電壓 VT 下降。

DIBL 系數 = ΔVT / ΔVDS

單位:mV/V

該系數定量描述每單位 VDS 上升所引起的 VT 降低量;理想情況下應為 0。

DIBL 還會使亞閾值斜率(SS)變差,即其數值增大。

Short Channel Effect (SCE)

Vtsat, Vtlin, Vtgm:三種MOSFET閾值電壓對比

溝道越短,漏極電場向源端的穿透就越強;

因此,短溝道器件會表現出更顯著的 DIBL 漂移。

當器件體區減薄時,漏極電場向源端穿透的程度會因體區耗盡區的“擠壓”而減弱,從而抑制 DIBL。

為進一步改善 DIBL,還可采用以下工藝/結構策略:

淺結源/漏(Shallow S/D junctions),

暈環(Halo)與倒阱(Retrograde wells)離子注入。

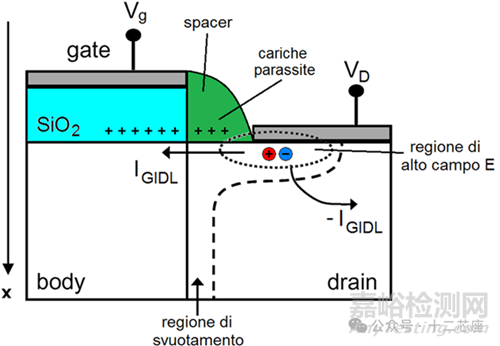

GIDL

Gate Induced Drain Leakage (GIDL)

知識日記:GIDL, Gate Induced Drain Leakage, 柵致漏極泄漏電流

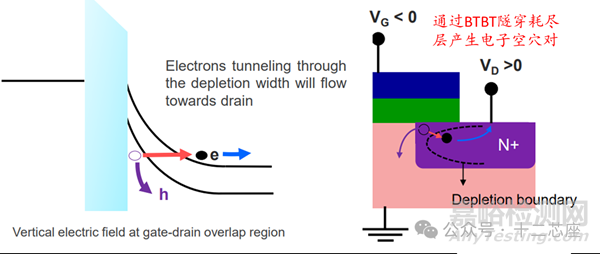

柵極感應漏極漏電流(GIDL)通常發生在柵極被偏置到積累區、同時漏極被施加反向高電壓的情形下。

此時,在柵-漏(N+)重疊區域,器件被迫進入深耗盡狀態:柵極處于積累偏壓,漏極處于反向偏置。

柵-漏重疊區內跨越柵氧的強垂直電場使價帶中的電子發生帶-帶隧穿,躍遷至導帶,從而產生 GIDL。

免責聲明:作者尊重知識產權、部分圖片和內容來源于公開網絡,版權歸原撰寫發布機構所有,如涉及侵權,請及時聯系刪除。

Reference:

1. Fundamental of Modern VLSI Devices, Yuan Taur and Tak H. Ning

2. Modern Semiconductor Devices for Integrated Circuits, Chenming Hu

3. Semiconductor Fundamentals, Robert F. Pierret

4. Semiconductor Physics and Devices, Donald Neamen

5. Physics of Semiconductor Devices, Simon Sze6. Micron