引言

在集成電路設計中,版圖(Layout)是連接電路原理圖與實際芯片制造的關鍵環節。一個優秀的版圖設計不僅要實現電路功能,更要優化性能、減小寄生效應、提高良率。 本文將通過圖例,帶您了解芯片設計中幾種典型器件的版圖構成。

1. 電阻器(Resistor)Layout圖例

電阻器是集成電路中最基本的無源器件之一。在版圖設計中,電阻器的阻值由其材料的薄層電阻(Sheet Resistance)和幾何形狀決定。以下圖例展示了不同形狀的電阻以及其阻值計算。

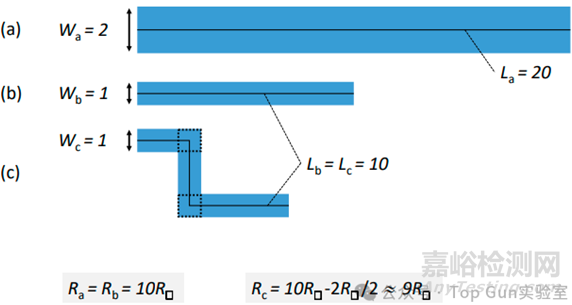

1.1 薄層電阻與電阻形狀

上圖展示了三種不同形狀的導電薄膜:

(a) 直線形電阻:寬度Wa=2,長度La=20。

(b) 直線形電阻:寬度Wb=1,長度Lb=10。

(c) L形電阻:由兩段寬度Wc=1,長度Lc=10的導電薄膜組成。由于L形轉角處的電流分布不均勻,其有效電阻Rc≈9R□,略小于簡單的長度疊加計算結果。

這說明在實際版圖設計中,需要考慮轉角等幾何效應,以精確控制電阻值。但芯片的電阻通常是不準確的(有很多因素會影響阻值精度),設計者更多是使用電阻比例來替代直接使用電阻值。

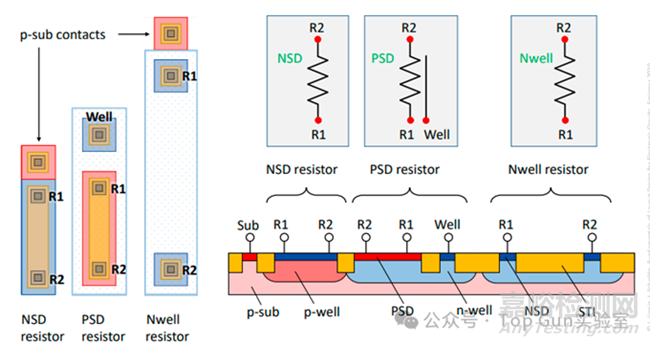

1.2 不同類型的集成電阻器

上圖展示了三種常見的集成電阻器類型及其版圖和截面示意圖:

NSD電阻器:利用n+擴散區作為電阻體。

PSD電阻器:利用p+擴散區作為電阻體。

Nwell電阻器:利用N阱作為電阻體。

這些電阻器在版圖上通過接觸孔(Contact)與金屬層連接。選擇不同類型的電阻器取決于 所需的阻值范圍、精度、溫度系數以及與工藝的兼容性。

2. MOSFET(金屬氧化物半導體場效應晶體管)Layout圖例

MOSFET是集成電路中最核心的器件,其版圖設計直接影響電路的性能。以下圖例展示了MOSFET的平面版圖、截面圖以及其對應的電路符號。

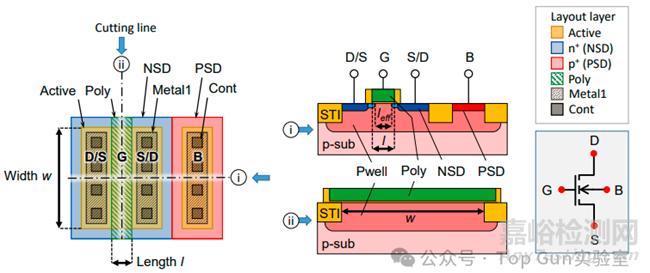

2.1 NMOS晶體管的版圖與結構

上圖展示了一個NMOS晶體管的版圖(左側)、兩個不同方向的截面圖(中間)以及其電路 符號(右側)。

版圖(Layout):

從上方俯視,可以看到不同層(如Active、Poly、Metal1、Cont) 的幾何形狀和相對位置。其中,Poly(多晶硅)層形成柵極(G),Active(有源區)形成源極(S)和漏極(D),并通過Cont(接觸孔)和Metal1(金屬1)與外部電路連接。B表示襯底連接。

截面圖(Sectional View):

截面(i)展示了柵極、源極、漏極以及襯底的垂直結構,可以看到有效溝道長度(l_eff)和柵極長度(l)。 截面(ii)展示了晶體管的寬度(w)。

2.2 PMOS晶體管的版圖與結構

與NMOS類似,上圖展示了一個PMOS晶體管的版圖、截面圖和電路符號。 PMOS晶體管通常構建在N阱(Nwell)中,其源極和漏極是p+擴散區(PSD)。

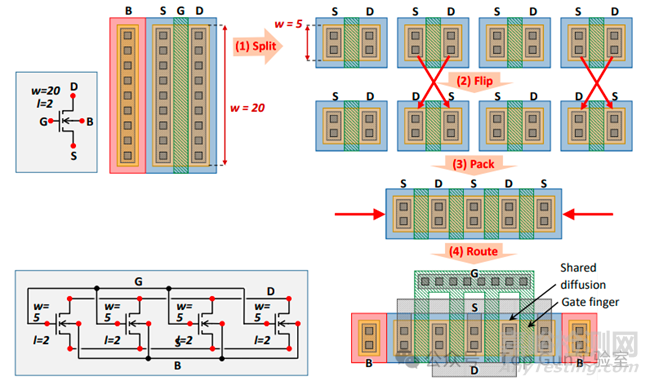

2.3 MOSFET的多指結構與布局技巧

當需要設計大尺寸MOSFET時,通常會采用多指結構(Multi-finger Structure),即將一個大尺寸晶體管分解為多個并聯的小尺寸晶體管。這種方法有以下優點:

降低寄生效應:減小柵極電阻和寄生電容。

改善匹配性:通過交錯排列(Interdigitation)等布局技巧,提高器件之間的匹配精度。

散熱:有助于分散熱量,改善器件的可靠性。

上圖展示了一個W=20,L=2的MOSFET如何通過“分裂(Split)”、“翻轉(Flip)”、“堆疊 (Pack)”和“布線(Route)”等步驟,形成一個由多個W=5,L=2的小尺寸晶體管組成的多指結構。這種布局技巧在模擬電路中非常常見,用于優化器件性能和版圖面積。

3. 電容器(Capacitor)Layout圖例

電容器在模擬電路中用于濾波、耦合、頻率補償等。集成電路中的電容器有多種實現方式, 以下展示幾種常見的電容器版圖。

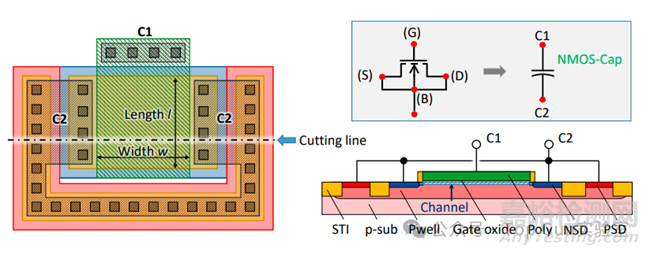

3.1 NMOS電容器

NMOS電容器利用MOSFET的柵極與溝道之間的電容效應。上圖展示了NMOS電容器的版圖、截面圖以及其電路符號。其中,C1和C2分別代表電容器的兩個端點。

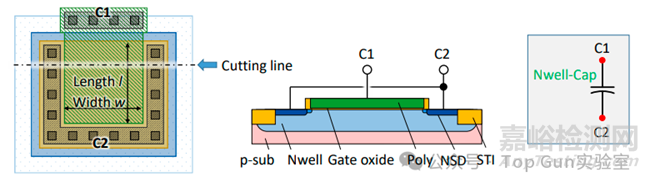

3.2 Nwell電容器

Nwell電容器利用N阱與襯底之間的PN結電容。上圖展示了Nwell電容器的版圖、截面圖以及其電路符號。這種電容器通常具有較低的電容密度,但可以提供較大的電容值。

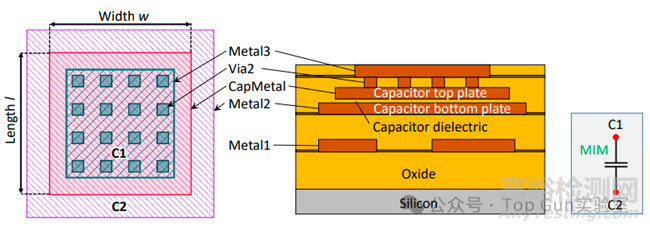

3.3 MIM(Metal-Insulator-Metal)電容器

MIM電容器是利用兩層金屬之間夾一層介質形成的電容器,具有較高的電容密度和較好的線性度。上圖展示了MIM電容器的版圖、截面圖以及其電路符號。通常,MIM電容器由多層金屬和介質堆疊而成,以實現更大的電容值。

總結

通過對電阻器、MOSFET和電容器這三種典型集成電路器件的版圖圖例解析,我們可以看到,模擬集成電路的版圖設計是一項精細且充滿挑戰的工作。它不僅需要深厚的電路知識, 更需要對半導體工藝和版圖技巧的深刻理解。每一個器件的布局、尺寸和互連方式都可能對最終的電路性能產生決定性的影響。