您當前的位置:檢測資訊 > 科研開發

嘉峪檢測網 2025-08-20 22:06

鎖相環(Phase-Locked Loop, PLL)作為現代電子系統的核心組件,在時鐘生成、頻率合成和信號處理等領域扮演著關鍵角色。從智能手機的射頻前端到高精度儀器的頻率源,PLL 以其獨特的相位反饋機制實現了對輸出信號的精確控制。

本文將系統解析 PLL 的工作原理,深入探討其核心模塊的設計要點,并結合工程實踐中的挑戰,提供從理論到應用的完整設計指南。

PLL 的基本原理與架構

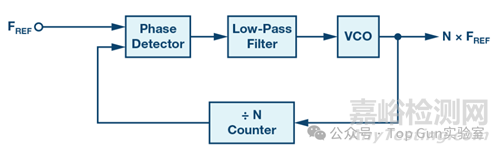

PLL 的本質是一個負反饋控制系統,通過動態調整輸出信號的相位和頻率,使其與參考信號保持同步。其基本架構包含四個核心模塊:鑒頻鑒相器(PFD)、電荷泵(CP)、環路濾波器(LPF)和壓控振蕩器(VCO),以及反饋分頻器。當系統處于鎖定狀態時,輸出頻率 FO 與參考頻率 FREF 滿足FO = N* FREF,其中N為反饋分頻比。

鑒頻鑒相器與電荷泵的協同工作鑒頻鑒相器是 PLL 的 “相位感知” 核心,其典型結構由兩個 D 觸發器和一個延遲元件組成。當參考信號(+IN)與反饋信號(-IN)存在頻率差時,PFD 會產生持續的 “向上” 或 “向下” 脈沖:若 + IN 頻率高于 - IN,PFD 輸出高電平脈沖,驅動電荷泵向環路濾波器注入正電流;反之則注入負電流。這種電流脈沖的持續時間反映了相位差的大小,而極性則由頻率差的方向決定。

電荷泵作為 PFD 與環路濾波器之間的接口,將相位差轉換為電流信號。理想情況下,電荷泵應具備快速開關能力和低泄漏電流,以確保相位誤差被準確轉換為電壓控制信號。

環路濾波器與壓控振蕩器的頻率控制

環路濾波器作為 PLL 的 “低通濾波” 環節,對電荷泵輸出的電流脈沖進行積分,生成平滑的 VCO 調諧電壓。其帶寬選擇是 PLL 設計的關鍵權衡點:窄帶寬(如 < 1kHz)能有效抑制參考源和 PFD 引入的帶內噪聲,但會延長鎖定時間;寬帶寬則反之,適用于需要快速頻率切換的場景(如跳頻通信)。

壓控振蕩器是 PLL 的 “頻率執行器”,通過變容二極管等可調元件實現頻率與電壓的線性轉換。VCO 的核心指標是相位噪聲,其質量因子(Q 值)決定了噪聲水平:高 Q 值電路在 100kHz 偏移處相位噪聲可達 - 115dBc/Hz,但頻率覆蓋范圍較窄;寬頻 VCO雖覆蓋 4-8GHz,但相位噪聲惡化至 - 100dBc/Hz。

PLL 的核心架構與技術演進

隨著應用場景的擴展,PLL 架構從基礎整數 N 型發展出分數 N 型,以平衡頻率分辨率和相位噪聲性能。兩種架構的差異直接影響系統設計的關鍵參數選擇。

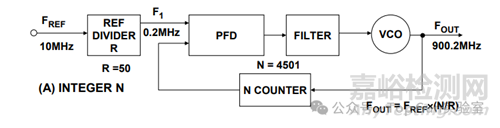

整數 NPLL:簡單性與噪聲挑戰

整數 NPLL 的輸出頻率嚴格為參考頻率的整數倍,適用于頻率步進較大的場景(如固定頻率時鐘生成)。其反饋分頻比 N 為整數,設計中需注意:當N 值較高時,帶內相位噪聲按 20log(N) 惡化。例如,在 1.8GHz 輸出場景中,整數 N PLL 采用 13MHz 參考頻率時,FOM(品質因數)計算為 - 223 + 10log (13MHz) + 20log (138) = -109dBc/Hz,優于同條件下的分數 N PLL。

整數 N 架構的雜散主要來源于 PFD 頻率及其諧波,可通過窄帶環路濾波器抑制。但當需要小頻率步進(如 GSM 通信中的 200kHz 間隔)時,整數 NPLL 被迫采用低參考頻率,導致 N值飆升至 9000 以上,帶內噪聲惡化至 - 91dBc/Hz,此時分數 N 架構成為更優選擇。

分數 NPLL:分辨率與噪聲的平衡藝術

分數 N PLL 通過引入小數分頻比(如 N = NINT + NFRAC/MOD ),在保持高參考頻率的同時實現精細頻率步進。以 5G 本地振蕩器設計為例,HMC704 分數 N PLL 采用 50MHz PFD 頻率,將 N 值從整數 N 架構的 7400 降至 148 + 0/50,使 8kHz 偏移處的相位噪聲從 - 90.5dBc/Hz 改善至 - 105.7dBc/Hz,提升 15dB。

分數 N 技術的核心是通過 Σ-Δ 調制器對瞬時分頻比進行平均,但其代價是引入分數雜散。當分頻比接近整數邊界時,雜散尤為顯著,需通過調整參考頻率或優化 VCO 輸出緩沖來抑制。

PLL 設計的工程實踐與關鍵步驟

從指標到架構的系統規劃

設計伊始需明確核心指標:參考頻率 F_REF、輸出頻率范圍、頻率步進、相位噪聲、鎖定時間和雜散抑制。對于固定頻率應用(如時鐘凈化),整數 N PLL 因低噪聲優勢成為首選;而對于需要小步進的場景(如通信頻段切換),分數 N 架構更具優勢。

以 1.8GHz 輸出、200kHz 步進的 GSM 系統為例:若采用整數 N PLL,需將參考頻率設為 200kHz,導致 N = 9000 ,帶內噪聲惡化至 - 91dBc/Hz;而分數 N PLL 可采用 13MHz 參考頻率,通過 N = 138 + N_FRAC/65 實現 200kHz 步進,帶內噪聲維持在 - 106dBc/Hz。

環路濾波器的參數優化

環路濾波器設計需平衡相位噪聲、鎖定時間和穩定性。典型設計步驟如下:

帶寬選擇:通常設為 PFD 頻率的 1/10 以下,如 50MHz PFD 對應帶寬≤5MHz;

相位裕度:目標設為 45°-60°,以避免濾波器諧振峰值引入額外抖動;

元件選型:使用高精度電阻電容(誤差≤1%),并盡量靠近 PLL 芯片布局,減小寄生效應。

PCB 布局與調試的關鍵要點

PCB 布局對 PLL 性能至關重要,需遵循以下原則:

信號完整性:參考輸入端口需匹配阻抗(如 50Ω),并聯電容應盡可能小,避免降低信號 slew rate;

電源分離:模擬與數字電源嚴格分離,VCO 電源尤其敏感,需采用低噪聲 LDO(如噪聲密度 < 10nV/√Hz);

元件靠近:環路濾波器元件(R、C)緊鄰 PLL 芯片放置,反饋路徑盡量短,減少寄生電感。

調試階段可借助 MUXOUT 引腳監測內部狀態:通過查看 R 計數器輸出確認參考信號有效性,觀察 N 分頻器輸出驗證反饋路徑正確性。時域分析需用示波器檢查 SPI 時序,確保數據建立時間滿足規范(輸入高電壓≥1.5V,低電壓≤0.6V)。頻譜分析則關注相位噪聲曲線與雜散點,若實測值與仿真不符,需排查環路濾波器元件值偏差或參考源噪聲超標。

高性能 PLL 的應用與前沿挑戰

5G 通信中的窄帶 LO 設計

5G 系統對 PLL 的關鍵指標是誤差矢量幅度(EVM)和 VCO 阻塞性能。EVM 反映調制信號的失真程度,對于 64-QAM 調制需≤8%,這要求 PLL 在 1kHz-100MHz 偏移范圍內的集成相位噪聲足夠低。VCO 阻塞性能則關乎接收機抗干擾能力:若 VCO 相位噪聲過高,800kHz 外的強干擾信號(-25dBm)可能混疊至接收頻段,淹沒 - 101dBm 的弱信號。

低抖動時鐘的精密設計

高速 ADC/DAC 對采樣時鐘的抖動極為敏感,如 12 位 ADC 要求時鐘抖動 < 100fs,否則信噪比(SNR)將劣化。設計低抖動時鐘 PLL 需注意:

低 N 值優先:固定頻率應用中,選擇 F_REF為輸出頻率的整數因子,如輸出 1GHz 時鐘時采用 100MHz 參考, N = 10 ;

環路優化:使 PLL 帶內噪聲與 VCO 噪聲在中頻處相交,實現最小抖動;

相位裕度:保持 60° 左右,避免濾波器峰值引入額外抖動。

來源:Internet