您當(dāng)前的位置:檢測(cè)資訊 > 科研開發(fā)

嘉峪檢測(cè)網(wǎng) 2024-10-26 11:45

各階段常見的典型失效機(jī)理

前段制程(FEoL)常見的失效機(jī)理

1)與時(shí)間相關(guān)的電介質(zhì)擊穿(TDDB)-- 柵極氧化物

2)熱載流子注入(HCI)

3)負(fù)偏壓溫度不穩(wěn)定性(NBTI)

4)表面反轉(zhuǎn)(移動(dòng)離子)

5)浮柵非易失性存儲(chǔ)器數(shù)據(jù)保持

6)局部電荷捕獲非易失性存儲(chǔ)器數(shù)據(jù)保持

7)相變(PCM)非易失性存儲(chǔ)器數(shù)據(jù)保持

后段制程(BEoL)常見的失效機(jī)理

1)與時(shí)間相關(guān)的電介質(zhì)擊穿(TDDB)-- 層間電介質(zhì)/低k值/移動(dòng)銅離子

2)鋁電遷移(Al EM)

3)銅電遷移(Cu EM)

4)鋁和銅腐蝕

5)鋁應(yīng)力遷移(Al SM)

6)銅應(yīng)力遷移(Cu SM)

封裝/界面常見的失效機(jī)理

1)因溫度循環(huán)和熱沖擊導(dǎo)致的疲勞失效

2)因溫度循環(huán)和熱沖擊導(dǎo)致的界面失效

3)因高溫導(dǎo)致的金屬間化合物和氧化失效

4)錫須

5)離子遷移動(dòng)力學(xué)(PCB)--組件清潔度

本文對(duì)FEoL階段的相變(PCM)非易失性存儲(chǔ)器數(shù)據(jù)保持模型進(jìn)行研究

在FD-SOI和FinFET CMOS技術(shù)中,傳統(tǒng)浮柵非易失性存儲(chǔ)器(NVM)集成在28nm和更小的制程上是一個(gè)重大的技術(shù)挑戰(zhàn)。新的NVM技術(shù)基于特殊外來材料的功能特性,采用了與Flash存儲(chǔ)器技術(shù)完全不同的物理機(jī)制,為28nm CMOS轉(zhuǎn)變帶來的工藝集成困難提供了更有效的解決方案。在這些常被稱為“新興存儲(chǔ)器”的新型NVM技術(shù)中,最成熟的是相變存儲(chǔ)器(PCM)。

相變記憶的基本機(jī)制是由斯坦福·羅伯特·奧夫斯基在20世紀(jì)60年代發(fā)明的,PCM通過諸如鍺銻碲(GeSbTe)之類的薄膜硫族化物材料的電阻變化來存儲(chǔ)數(shù)據(jù),最常見的成分比例為Ge2Sb2Te5(GST)。

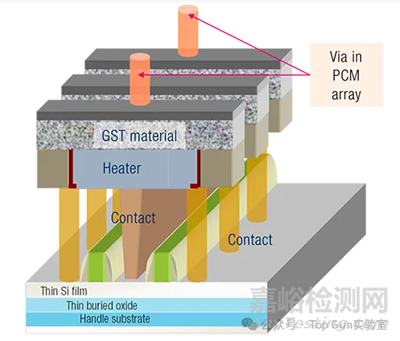

PCM的顯著特點(diǎn)是薄膜層的電阻變化與材料在晶態(tài)和非晶態(tài)之間的熱致相變有關(guān),非晶態(tài)具有高電阻率,而晶態(tài)具有顯著較低的電阻率。在PCM中,熱刺激由施加在兩個(gè)電極之間的電脈沖提供,這兩個(gè)電極與位于它們之間的相變材料直接接觸,電脈沖的形狀和幅度決定了相變層是轉(zhuǎn)變?yōu)榉蔷B(tài)還是晶態(tài),存儲(chǔ)器的狀態(tài)是通過在低電場(chǎng)下測(cè)量其電阻來確定。PCM陣列截面圖如下圖所示。

單比特每單元(single-bit-per-cell,SBC)有兩個(gè)狀態(tài):SET和RESET。

1)SET狀態(tài):晶態(tài)(低電阻)的SET狀態(tài)在熱力學(xué)上是穩(wěn)定的;

2)RESET狀態(tài):高電阻的非晶相有兩個(gè)獨(dú)立的電阻變化機(jī)制--結(jié)晶和電阻漂移。

漂移過程是由于硫族化物的結(jié)構(gòu)重排和本征陷阱的動(dòng)力學(xué)導(dǎo)致非晶相電阻率的穩(wěn)定增加。由于漂移過程增加了高電阻非晶態(tài)的電阻,所以它不會(huì)導(dǎo)致SBC PCM器件的數(shù)據(jù)丟失。而結(jié)晶會(huì)導(dǎo)致電阻下降,因此結(jié)晶會(huì)導(dǎo)致PCM器件狀態(tài)變化,造成器件數(shù)據(jù)丟失。

故PCM的數(shù)據(jù)保持能力可理解為避免非晶材料不期望的再結(jié)晶來保持高電阻RESET狀態(tài)的能力。

相變(PCM)非易失性存儲(chǔ)器數(shù)據(jù)保持模型:

如前文所述,相變存儲(chǔ)器的晶態(tài)在熱力學(xué)上是穩(wěn)定的。非晶態(tài)會(huì)在溫度條件下慢慢的通過固態(tài)非晶相中的晶核形成和晶體生長(zhǎng)轉(zhuǎn)變?yōu)榫B(tài)。為保證在存儲(chǔ)設(shè)備的使用期限和使用條件下的數(shù)據(jù)保留,非晶態(tài)到晶態(tài)的結(jié)晶時(shí)間必須足夠長(zhǎng)。用于相變存儲(chǔ)器的Ge2Sb2Te5相變合金的結(jié)晶遵循阿倫尼烏斯定律,在正常使用溫度下非晶態(tài)到晶態(tài)的結(jié)晶時(shí)間為數(shù)年;因此,需要在高溫下進(jìn)行加速實(shí)驗(yàn),以有效評(píng)估活性材料的結(jié)晶特性。

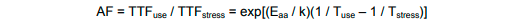

在PCM中,當(dāng)一個(gè)最初被編程為高電阻RESET狀態(tài)的單元在后續(xù)的讀取操作中被發(fā)現(xiàn)處于低電阻SET狀態(tài)時(shí),那就發(fā)生了數(shù)據(jù)丟失(電阻下降到低于有效閾值失效電阻RFail時(shí),RFail值取決于存儲(chǔ)陣列中的傳感算法)。電阻下降到低于RFail所需的時(shí)間被稱為故障時(shí)間(TTF)。對(duì)于相對(duì)較低的溫度(小于 200°C),晶核形成和生長(zhǎng)機(jī)制都由原子擴(kuò)散勢(shì)壘和結(jié)晶動(dòng)力學(xué)控制,可以用阿倫尼烏斯定律近似模型。其表達(dá)式為:

保留損失的熱加速因子是通過將使用條件下的故障時(shí)間除以高溫應(yīng)力下的故障時(shí)間得到的:

注:該模型適用于SBC PCM器件,該模型僅考慮了通過結(jié)晶(相變存儲(chǔ)器材料的固有屬性)導(dǎo)致的數(shù)據(jù)丟失,不適用與可能遇到的所有缺陷機(jī)制。

開發(fā)PCM的加速模型時(shí),應(yīng)考慮PCM的以下特性:

1)首先,在測(cè)試結(jié)構(gòu)或?qū)iT設(shè)計(jì)的特性陣列中,通常在烘烤溫度下監(jiān)測(cè) PCM 電阻,以實(shí)現(xiàn)更大的加速。在這種情況下,非晶態(tài)電阻率對(duì)溫度的相關(guān)性和漂移現(xiàn)象的結(jié)合會(huì)改變RFail,導(dǎo)致計(jì)算出的Eaa出現(xiàn)誤差。可靠的Eaa提取應(yīng)通過在較長(zhǎng)時(shí)間(較低烘烤溫度)進(jìn)行多次測(cè)量,并將陣列冷卻至固定溫度進(jìn)行所有電阻測(cè)量來獲得。

2)其次,PCM數(shù)據(jù)丟失一個(gè)被廣泛接受的物理模型是通過所得混合相結(jié)構(gòu)的類滲流傳導(dǎo)。對(duì)同一器件進(jìn)行重復(fù)保留測(cè)量的實(shí)驗(yàn)結(jié)果顯示數(shù)據(jù)保持時(shí)間不同,從而證明了GST結(jié)晶的隨機(jī)成分。因此,PCM數(shù)據(jù)保持時(shí)間預(yù)計(jì)具有隨機(jī)性,因此需要對(duì)數(shù)據(jù)保持時(shí)間數(shù)據(jù)進(jìn)行統(tǒng)計(jì)分析,研究表明該數(shù)據(jù)遵循威布爾統(tǒng)計(jì)。在提取Eaa時(shí),需要進(jìn)行充分的抽樣,以滿足威布爾統(tǒng)計(jì)數(shù)據(jù)的要求。

3)最后,關(guān)于PCM合金Ge2Sb2Te5的研究數(shù)據(jù)表明,擦/寫循環(huán)對(duì)數(shù)據(jù)保持的影響相對(duì)較小(在某些情況下實(shí)際上改善了數(shù)據(jù)保持)。然而這種表現(xiàn)可能取決于特定的PCM合金或技術(shù)。因此,作為鑒定程序的一部分,應(yīng)在循環(huán)之前和之后進(jìn)行數(shù)據(jù)保留和加速模型分析。

注:JEDEC標(biāo)準(zhǔn)JESD91A,《Method for Developing Acceleration Models for Electronic Component Failure Mechanisms》,為測(cè)量提取Eaa提供了參考程序。

相變(PCM)非易失性存儲(chǔ)器數(shù)據(jù)保持壽命預(yù)估示例:

目標(biāo):

計(jì)算加速因子(AF),即AF=TTFuse/TTFaccel;對(duì)由于非晶RESET狀態(tài)下結(jié)晶而導(dǎo)致的PCM數(shù)據(jù)丟失的應(yīng)力進(jìn)行一次加速壽命計(jì)算。

假設(shè)條件:

1)正常使用條件為:55°C芯片溫度

2)加速條件為:85°C

3)Ge2Sb2Te5表觀活化能Eaa:2.5eV

AF計(jì)算公式:

AF=tretention,use/tretention,stress

AF=exp[(Eaa/k)(1/Tuse–1/Tretention,stress)]

假設(shè)條件代入計(jì)算:

AF=exp[(2.5eV/8.62x10–5eV/K)(1/(273+55)K–1/(273+85)K)]=1637

結(jié)論:對(duì)于 PCM 數(shù)據(jù)保持,在85°C下烘烤100h的選擇相當(dāng)于在55°C的使用條件下163,700h(18.7年)。

相關(guān)文獻(xiàn):

1)S. Lai and T. Lowrey, “OUM—A 180 nm nonvolatile memory cell element technology for stand alone and embedded applications,” IEDM Tech. Dig., 2001, pp. 803–806.

2)F. Pellizzer et al., “A 90 nm phase change memory technology for standalone non-volatile memory applications,” Symp. on VLSI Tech., 2006, pp. 122–123.

3)S.H. Lee, Y.N. Hwang, S.Y. Lee, K.C. Ryoo, S.J. Ahn, H.C. Koo, C.W. Jeong, Y.T. Kim, G.H. Koh, G.T. Jeong, H.S. Jeong, and K. Kim,” Full Integration and Cell Characteristics for 64 Mb Nonvolatile PRAM”, Symp. on VLSI Tech., 2004, pp. 20-21.

4)G.W. Burr, M.J. Breitwisch, M. Franceschini, D. Garetto, K. Gopalakrishnan, B. Jackson, B. Kurdi, C. Lam, L.A. Lastras, A. Padilla, B. Rajendran, S. Raoux, and R.S. Shenoy, “Phase Change Memory Technology,” J. Vac. Sci. Technol. B Volume 28, Issue 2, pp. 223-262 (March 2010).

5)A. Pirovano, A. L. Lacaita, F. Pellizzer, S. A. Kostylev, A. Benvenuti, and R. Bez, “Low-field amorphous state resistance and threshold voltage drift in chalcogenide materials,” IEEE Trans. Electron Devices, vol. 51, no. 5, pp. 714–719, May 2004.

6)A. Redaelli, D. Ielmini, U. Russo, and A. L. Lacaita, “Intrinsic data retention in nanoscaled phase-change memories—Part II: Statistical analysis and prediction of failure time,” IEEE Trans. Electron Devices, vol. 53, no. 12, pp. 3040–3046, Dec. 2006.

7)Y.N. Hwang, C.Y. Um, J.H. Lee, C.G. Wei, H.R. Oh, G.T. Jeong, C.H. Kim, and C.H. Chung, “MLC PRAM with SLC Write-speed and Robust Read Scheme,” Symp. on VLSI Tech.,2010 pp. 201-202

8)A. Redaelli, A. Pirovano, I. Tortorelli, D. Ielmini, and A. L. Lacaita. “A Reliable Technique for Experimental Evaluation of Crystallization Activation Energy in PCMs”. IEEE Electr. Dev. Lett., 29(1): pp 41-43 (2008).

9)U. Russo, D. Ielmini, A. Redaelli, and A. L. Lacaita, “Intrinsic data retention in nanoscaled phase-change memories—Part I: Monte Carlo model for crystallization and percolation,” IEEE Trans. Electron Devices, vol. 53, no. 12, pp. 3032–3039, Dec. 2006.

10)B. Gleixner, A. Pirovano, J. Sarkar, F. Ottogalli, E. Tortorelli, M. Tosi, R. Bez, “Data retention characterization of phase-change memory arrays,” IRPS Tech. Dig., 2007, pp. 542–546.

11)B. Gleixner, F. Pellizzer, R. Bez, "Reliability characterization of Phase Change Memory" NonVolatile Memory Technology Symposium (NVMTS), 2009 pp. 7 - 11

12)A. Redaelli, D. Ielmini, A. L. Lacaita, A. Pirovano, F. Pellizzer, and R. Bez, “Impact of crystallization statistics on data retention for phase change memories,” IEDM Tech. Dig., 2005, pp. 742-745.

13)J. W. Christian, The Theory of Transformation in Metals and Alloys. New York: Pergamon, 1965.

14)U. Russo, D. Ielmini, and A. L. Lacaita, “A physics-based crystallization model for retention in phase-change memories,” Proc. IRPS Tech. Dig., 2007, pp. 547–553.

來源:Top Gun實(shí)驗(yàn)室