您當前的位置:檢測資訊 > 科研開發

嘉峪檢測網 2025-05-19 09:12

DRAM(Dynamic Random Access Memory)如同中轉站,在CPU或GPU進行數據運算時,承擔起臨時存儲數據的重任,其性能取決于處理器訪問速度及數據單元排列緊密度。

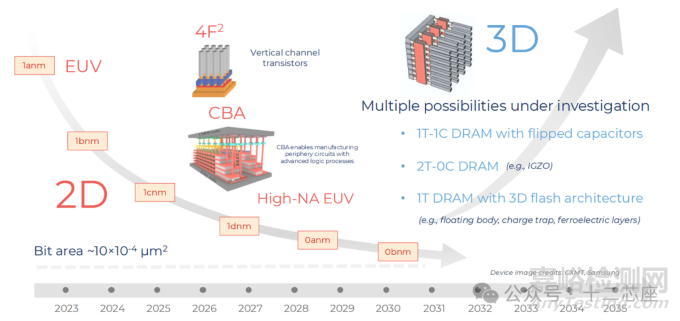

而目前3D DRAM 無疑是提高cell density 的新手段,對于3D DRAM這一概念,也有兩種截然不同的做法,其中一種就是如今最為火熱的HBM,不過,HBM是堆疊芯片(stacked-die)存儲器,并非是像3D NAND那樣的單片3D芯片,其介于2D和3D之間,也有人將它劃分進了2.5D的范疇。

至于真正的單片3D芯片,為了提高存儲密度,需要減少單層DRAM芯片的單元面積,但垂直電容器導致層非常厚,堆疊困難,部分方案嘗試將電容器水平放置,也有的方案徹底取消電容器。

Fig1. 下一代動態隨機存取存儲器 - 技術路線圖

DRAM的基本構造

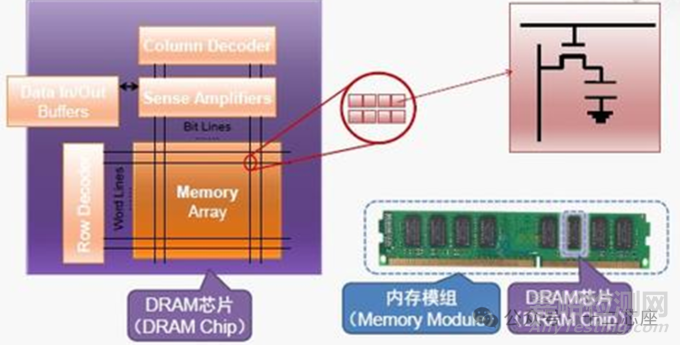

存儲數據的基本單位——存儲單元(Cell)至關重要。單元面積越小,有限空間內集成的單元就越多,電信號傳輸距離也越短,低功耗效率和處理速度得以提升。每個單元由MOS晶體管和電容器組成,前者控制電流方向與電壓,后者負責短暫充放電存儲數據。

Fig2. DRAM的基本構造

為存儲海量數據,DRAM將無數單元以棋盤格形式排列成陣列(Array),借助解碼器(Decoder)指引,處理器可快速定位目標單元,位線(Bit Line, BL)連接源極并施加電壓,字線(Word Line, WL)連接柵極控制電壓,電容器與漏極垂直相連。

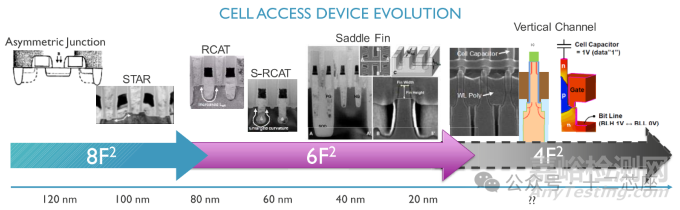

Fig3. Various cell access device options are shown.

Fig3. Various cell access device options are shown.

1.2D DRAM的演進

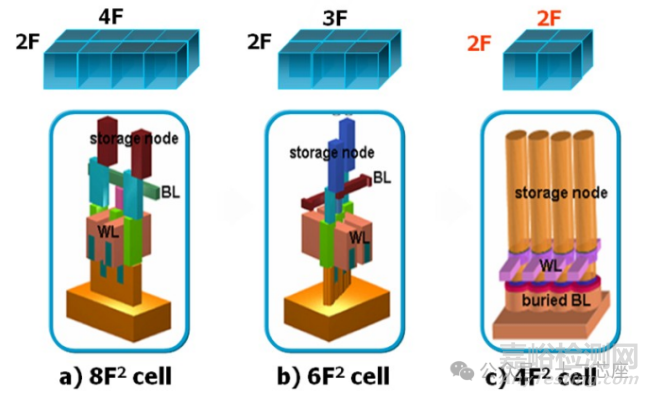

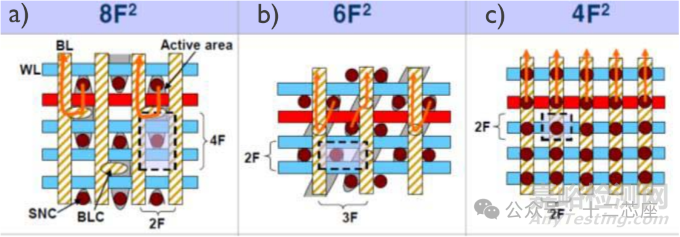

早期DRAM采用8F² RCAT結構,位線跨4格,字線跨2格,總面積8F²(F為最小特征尺寸),但源極無法直接與字線連接,需留白,單元實際占4格位線寬度。雖結構簡單,位線與字線留白卻限制存儲密度提升。單元結構已從 8F2 單元演變為 6F2 單元,因為按照下圖所示的設計規則,單元尺寸可降低多達 75%。這一變化帶來了諸多難題,例如開路位線噪聲以及因單元尺寸變小而帶來的挑戰。然而,這些問題通過引入低電阻材料、縮小存儲節點電容器的介電層以及隔離技術得以解決。

Fig4. from 8F2 to 4F2 cell.

自130納米及以下制程起,6F² BCAT結構登場,單元布局優化為位線3格、字線2格,大幅提升單元密度。然而,隨線路寬度縮小到10納米級,物理極限致電流泄漏、信號干擾頻發,平面棋盤格排列單元難以為繼。

2.3D DRAM的崛起

為高效利用有限面積,豎起水平排列單元或垂直堆疊單元陣列成必然選擇。4F²結構將源極、柵極、漏極轉為垂直結構,下層源極接位線,其上柵極連字線,再往上堆疊漏極與電容器,減少電氣干擾,面積縮約三分之一,如三星的垂直通道晶體管(VCT)DRAM和SK海力士的垂直柵極(VG)DRAM。

而3D DRAM則更進一步,讓位線或字線之一豎直排列,晶體管和電容器橫向堆疊,層層疊加,類似3D NAND,雖各家廠商在結構和堆疊技術上各有不同。

3.8F²、6F²、4F² 主要區別

8F² DRAM:

8F² DRAM 是傳統的主流 DRAM 架構,采用折疊位線架構。其單元設計對稱,位線對緊挨著,有助于實現可靠的檢測與恢復操作。這種架構在可制造性和 DRAM 陣列操作方面表現出色,能夠有效減少陣列噪聲的影響,確保數據讀取的準確性。然而,由于其單元面積較大,限制了存儲密度的進一步提升,難以滿足不斷增長的存儲需求。

6F² DRAM:

6F² DRAM 是一種改進的架構,單元面積比8F²減少了約25%。它采用開放位線架構,位線對由兩根分列在位線檢測放大器兩側的位線組成。這種設計可以在相同的芯片面積上集成更多的存儲單元,提高了存儲密度。然而,開放位線架構對陣列噪聲更敏感,可能會影響數據讀取的可靠性。此外,更小的單元尺寸也帶來了更高的制造工藝要求。

4F² DRAM:

4F² DRAM 是一種新型的架構,通過將晶體管和電容器垂直堆疊,進一步減小了單元面積。這種架構不僅能夠顯著減少電氣干擾,還能在有限的芯片面積上實現更高的存儲密度。此外,垂直架構還能完全抑制row hammer干擾,提高存儲器的穩定性和可靠性。目前,4F² DRAM 還處于研發階段,但其在高密度存儲和低功耗應用方面具有巨大的潛力。

Fig5. (a) 8F2, (b) 6F2, and (c) 4F2 design architecture.

控制電路的堆疊創新

在4F2和3D DRAM中,控制電路(周邊電路)的垂直堆至關重要若能像堆積木般疊加這些電路,芯片面積將進一步縮小。但需分開制作繪制有DRAM單元陣列和控制電路的晶圓,再進行晶圓對晶圓(W2W)鍵合或混合鍵合(Hybrid Bonding°)

3D DRAM的行業意義

目前AI芯片市場常用的高帶寬存儲器(HBM)存在物理限制,隨著芯片不斷堆疊,發熱和功率效率問題日益突出。行業正考慮基于3D DRAM重新設計下一代存儲器結構,3D DRAM的突破和發展無疑將為存儲器技術乃至整個半導體行業帶來新的活力與變革。

來源:十二芯座