您當前的位置:檢測資訊 > 行業研究

嘉峪檢測網 2025-05-12 09:31

1.引 言

作為一名在半導體封裝測試領域摸爬滾打了 21年的“Old Money”,我見證了這個行業從傳統2D芯片到如今復雜3D集成的飛速發展。記得有一次,我參與了一個高端芯片項目的封裝設計,當時我們遇到了一個棘手的散熱問題。傳統2D封裝無論如何優化,都無法滿足芯片的散熱需求,項目一度陷入僵局。就在我們幾乎要放棄的時候,3DIC封裝技術給了我們新的希望。通過將芯片垂直堆疊,并在中間加入微通道冷卻結構,我們不僅解決了散熱問題,還大幅提升了芯片性能。從那以后,我就深深意識到 3D IC 技術的巨大發展空間潛力,類似國貿大廈,向天上要空間。

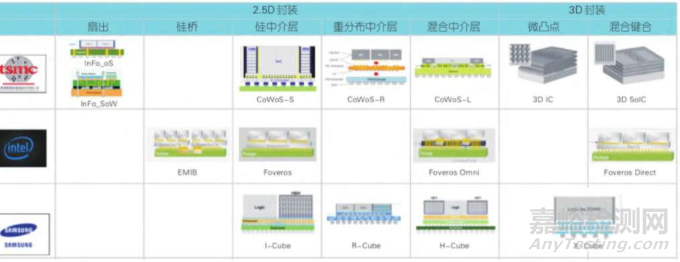

三巨頭 2.5D、3D 封裝工藝對照如下(附圖)

今天,我想和大家分享一下 3D IC 設計與封裝技術的最新進展、行業應用,以及未來的發展趨勢。

2.3D IC 設計與封裝技術的最新進展

(一)技術突破與創新

1. Cadence:打通從 Chiplet 到系統的完整 3D-IC 平臺生態

Cadence 的 Integrity™3D-IC 平臺是目前行業內唯一能覆蓋 Chiplet 設計、封裝規劃、system-level 分析的完整方案。它就像一個“超級管家”,從芯片的最初設計到最終的系統集成,都能提供一站式服務。這個平臺不僅支持數字、定制/模擬、熱分析工具,還全面覆蓋從芯片到系統的全流程設計需求。有了它,Engineers 可以更高效地完成復雜的設計任務,減少設計錯誤,縮短產品上市時間。

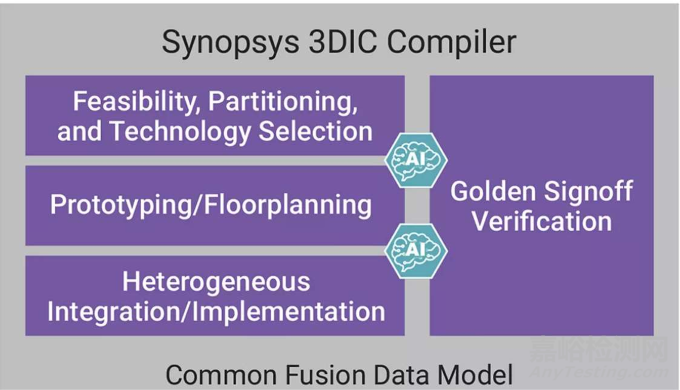

2. Synopsys:多物理場仿真與 AI 賦能設計

Synopsys 通過收購 Ansys,顯著提升了多物理場仿真能力。這就好比給設計師們配備 了一雙“透視眼”,能夠看到芯片在各種物理條件下的表現。其 3DIC Compiler 平臺與Ansys 的SI、Thermal landscape和可靠性sign off工具集成,為客戶提供芯片、封裝和系統級效應的黃金標準sign off精度。此外,Synopsys還引入了AI技術,讓設計過程更加智能化。AI可以根據歷史數據和設計規則,自動優化設計參數,提高設計efficiency 和質量。

3. Siemens EDA:系統級仿真與封裝技術

Siemens EDA(原 Mentor Graphics)在系統級仿真和封裝技術方面也持續創新。它的Xpedition™封裝設計工具就像一個“精密的拼圖大師”,能夠將不同的芯片和封裝組件完美地拼接在一起。同時,Siemens EDA 的 Calibre®平臺提供了從設計到制造的全流程驗證工具,支持 2.5D/3D 封裝技術。這就好比為芯片設計和制造過程安裝了一道“安全門”,確保每一個環節都符合設計要求。

(二)行業應用

1. HPC

3D IC技術在HPC領域大放異彩。以Intel的Foveros Direct 3D技術為例,它在數據中心GPU應用中支持8層芯片Stack,就像把8塊高性能的“磚塊”疊在一起,顯著提高了計算能力和數據傳輸速率。這種技術使得數據中心的服務器能夠更快地處理海量數據,為 AI、大數據分析等應用提供了強大的支持。

2. 消費電子

在消費電子領域,3D IC 技術讓我們的手機、平板電腦等設備變得更輕薄、更強大。

TSMC 的SoIC 技術(基于 CoWoS+WoW 的封裝方式)被應用于Apple A16 和 N2 芯片的堆疊,就像在芯片上搭建了一座“微型摩天大樓”,不僅提升了芯片性能,還為設備騰出了更多空間用于其他功能模塊。未來,隨著技術的不斷進步,我們的電子產品將變得更加智能、高效。

3. 汽車電子

汽車電子領域對可靠性和性能的要求極高。3D IC 技術在這里也大有可為。例如,ASE 的 TGV 技術用于 3D 電感封裝,就像給芯片穿了一件“防護服”,顯著提高了信號完整性和可靠性。這種技術在自動駕駛輔助系統和車載信息娛樂系統中發揮著重要作用,為我們的出行安全和便利提供了保障。

(三)行業報告與研究

1. CSPT(中國封裝協會)報告

根據中國封裝協會(CSPT) 的最新報告,中國在2.5D和3D封裝技術領域取得了顯著進展。國內廠商如JCET、HTtech等在先進封裝技術上持續突破,就像在半導體封裝的“賽道”上加速奔跑。預計到2025年,中國先進封裝市場規模將上漲至1137億元人民幣,這將為國內半導體產業的發展注入強大動力。

中國先進和傳統封裝規模趨勢分析如下(銷售口徑)

2. ICEPT(世界封裝協會)報告

ICEPT 的報告也顯示,3D IC 封裝技術的實用化開發正在全球范圍內加速推進。從2013年開始,3D IC 封裝技術的研究開發就涵蓋了多種應用場景,包括 3D 系統封裝、微波傳輸系統封裝、MEMS 設備制造等。這些技術的發展不僅推動了半導體行業的發展,也為其他高科技領域帶來了新的機遇。

3.未來發展趨勢

(一)更高集成度

未來,3D IC 技術將朝著更高集成度的方向發展。就像在芯片上搭建更高的“摩天大樓”,實現更多功能單元的堆疊。TSMC 預計到 2027 年,其 SoIC 技術將實現 3μm 間距,支持 8 層芯片堆疊。這意味著我們可以在更小的空間內實現更強大的功能,為未來的智能設備和高性能計算提供更強大的支持。

(二)更低功耗

隨著技術的不斷進步,3D IC 將進一步降低功耗。通過優化設計和制造工藝,例如 Intel 的 Foveros Direct 3D 技術,互連功耗降低至 0.15pJ/bit,相比傳統方案降低 30%。這不僅延長了設備的電池壽命,也為環保和可持續發展做出了貢獻。

(三)更廣泛應用

3D IC 技術將在更多領域得到應用,如 AI、量子計算、生物醫學等。例如,在 AI 領域,3D IC 可以實現更高的計算能力和更低的延遲,為智能算法的運行提供強大的硬件支持。在生物醫學領域,3D IC 可以用于開發微型化的醫療設備,為疾病的診斷和治療提供更精準的工具。

4.面臨的挑戰

(一) Heat dissipation

High - density stacking 帶來了散熱挑戰。就像在“摩天大樓”里安裝了太多的“發動機”,如果不解決散熱問題,IC 可能會因為過熱而損壞。Intel 開發的納米復合應力緩沖層, CTE 可調范圍達 3-7ppm/°C,為散熱問題提供了一種解決方案。

(二)TSV

TSV 的制造過程復雜,需要高精度的深孔刻蝕和金屬填充技術。TSV 內的缺陷可能導致信號傳輸問題,就像在“摩天大樓”的“電梯”里出現了故障。這需要進一步改進制造工藝,確保 TSV 的質量和可靠性。

(三) Rel of Bonding

鍵合技術需要確保芯片層間的物理連接和對齊,特別是在高溫和高濕度環境下。鍵合強度的穩定性是一個關鍵問題,就像“摩天大樓”的“地基”必須足夠堅固。這需要開發更先進的鍵合材料和技術,以提高鍵合的可靠性和穩定性。

5.總 結

3D IC 設計與封裝技術作為半導體行業的前沿領域,正在快速改變芯片制造和系統集成的未來。通過將多個芯片垂直堆疊,3D IC 技術不僅提高了集成度和性能,還顯著降低了功耗和尺寸。盡管面臨散熱、制造、鍵合等挑戰,但隨著技術的不斷進步,3D IC 將在更多領域得到廣泛應用,推動半導體行業的發展。未來,3D IC 技術將朝著更高集成度、更低功耗、更廣泛應用的方向發展,為高性能計算、消費電子、汽車電子等領域帶來更多的創新和突破。

參 考:

《Cadence whitepaper》

《集成電路封裝可靠性技術》

《Cadence Design Systems Annual Report 2022》

《基于SiP技術的微系統》

半導體國產替代三大核心賽道梳理

臺積電新一輪EDA訂單已鎖定:西門子、新思科技、Cadence、Ansys!

先進封裝:美國、中國、韓國最新進展盤點-電子工…

來源:芯片技術與工藝