您當前的位置:檢測資訊 > 科研開發

嘉峪檢測網 2025-05-07 18:57

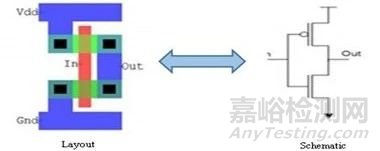

在集成電路(IC)設計領域,版圖與原理圖一致性檢查(LVS,Layout vs. Schematic) 是確保設計準確性和制造成功率的關鍵環節。它用于驗證芯片的物理版圖是否與設計原理圖保持一致,是實現電路功能正確性、保障產品質量的重要手段。

LVS檢查通過提取和比對兩種網表(netlist)—— 一份來自原理圖設計,另一份從版圖提取——來確保器件類型、數量、尺寸以及電氣連接關系完全一致。這一過程涵蓋了器件匹配、連通性驗證、端口一致性等多個層面,能夠有效發現諸如器件丟失、誤連、短路、開路或幾何誤差等隱藏問題。特別是在現代SoC或多模塊設計中,這種驗證尤為重要,因為一個細微的不一致都可能導致芯片功能失效或性能下降。

此外,LVS流程往往還與寄生參數提取(Parasitic Extraction)和版圖設計規則檢查(DRC)緊密結合。寄生電容、電阻等參數對高頻模擬電路或高速數字路徑影響顯著,而LVS確保其建立在正確的電氣結構基礎上,從而為后續時序分析、信號完整性分析打下堅實基礎。

擁有一套完善且高效的LVS驗證流程,不僅能夠在設計早期階段及時定位錯誤,避免問題流入流片階段,還能大幅減少反復修改和返工所造成的時間和成本損失。對芯片設計企業而言,LVS不僅是驗證環節,更是提升設計質量、優化流片成功率、加速產品上市周期的核心保障。

因此,LVS在現代IC設計流程中扮演著“設計閉環的守門人”角色。只有在LVS驗證無誤的前提下,設計才能進入Tape-out階段,邁向晶圓制造。這一環節的嚴謹性直接決定了設計交付的可靠性與最終芯片的成敗。

1.理解IC設計中的版圖與原理圖一致性驗證(LVS)

在集成電路(IC)設計中,版圖與原理圖一致性檢查(LVS,Layout versus Schematic) 是確保物理實現與設計意圖一致性的關鍵驗證步驟。通過對比版圖與原理圖,LVS不僅驗證電路結構的準確性,還直接影響到芯片的功能正確性、可制造性和最終產品的可靠性。

1.1 LVS檢查的核心組成部分

LVS驗證通常包括以下關鍵環節,每一項都為最終設計的一致性提供不同層面的保障:

網表對比(Netlist Comparison):將從原理圖生成的參考網表與從版圖提取的實際網表進行比對,確認電路中所有器件、端口及其連接關系是否一一對應,防止電路邏輯結構發生偏差。

寄生參數提取(Parasitic Extraction):通過提取金屬互連、電容、電阻等寄生參數,建立更為真實的電路模型,用于后續電路仿真與性能分析。例如,對于高速信號路徑或模擬電路,寄生電容的影響可能導致信號失真或相位漂移。( “寄生參數” (Parasitic Parameters)是指在電路設計與制造過程中,非理想因素所引入的額外電氣特性。這些參數不是電路設計者本意添加的,但由于物理結構、材料特性或制造工藝等原因而不可避免地存在。)

|

類型 |

解釋 |

常見來源 |

|

寄生電阻 (Parasitic Resistance) |

導線、電極等非理想導體存在一定電阻,會導致電壓下降、功耗增加 |

金屬布線、電極接觸、電源網絡路徑等 |

|

寄生電容 (Parasitic Capacitance) |

不同導體之間因空間距離過近而產生電容效應,可能引起信號延遲或耦合干擾 |

層間導線、晶體管柵極與襯底、金屬層之間 |

|

寄生電感 (Parasitic Inductance) |

電流變化時在導線中感生出的感應電壓,可能引發電源噪聲、信號完整性問題 |

電源線、長導線、封裝引腳 |

|

寄生器件效應 (Parasitic Devices) |

電路結構無意中形成了新的元器件,比如雙極晶體管或MOS結構,可能引發 latch-up 等問題 |

CMOS結構中的寄生晶體管、PNPN結構 |

設計規則檢查(DRC,Design Rule Checking):雖然DRC不直接比較原理圖與版圖,但作為輔助流程,它確保版圖在物理實現過程中遵守代工廠的幾何規則、間距規則和層次規則,是LVS之前的重要預處理環節之一。

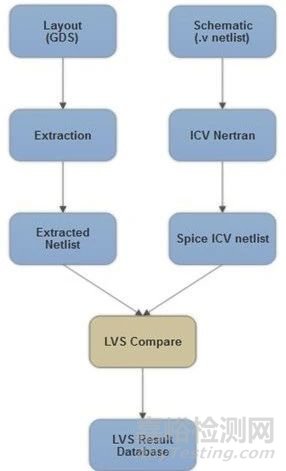

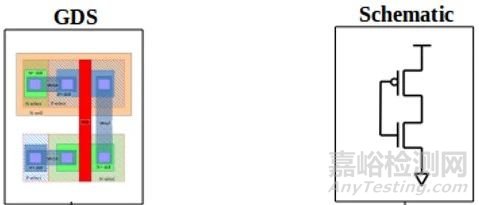

LVS(Layout Versus Schematic)流程主要包括版圖網表的提取與版圖與原理圖網表的比對兩個核心步驟。其流程如圖所示。

左側流程:Layout路徑(從GDS到版圖網表)

|

階段 |

步驟名稱 |

輸入 |

輸出 |

使用工具 / 模塊 |

關鍵說明 |

|

1 |

Layout (GDS) |

GDS 文件(GDSII Stream Format) |

布局物理數據(包含幾何結構、圖層、元件位置) |

IC版圖設計工具(IC Compiler II、Virtuoso) |

- GDS 是IC行業標準的版圖文件格式。 |

|

來源于IC布局工具(如IC Compiler II) |

- 記錄IC物理實現的圖層、形狀與元件布局。 |

||||

|

|

- 在LVS中作為版圖比對的輸入數據。 |

||||

|

2 |

Extraction(版圖提取) |

GDS 文件 |

版圖提取網表(Layout Netlist) |

LVS 工具的 Extraction 引擎 |

- 提取邏輯連接關系和器件信息(如MOS、電阻、電容等)。 |

|

規則庫(Rule Deck) |

(如Calibre、IC Validator) |

- 根據圖層定義與規則庫進行識別。 |

|||

|

|

|

- 可支持寄生參數提取(RC),但LVS中通常只關注拓撲結構。 |

|||

|

3 |

Extracted Netlist(提取網表) |

版圖提取結果(電氣連接+器件信息) |

Netlist 文件(Spice或SPF格式) |

LVS 工具 |

- 表示從物理版圖還原出的電路結構。 |

|

- 供后續與原理圖路徑生成的網表進行結構比對。 |

|||||

|

- 是實際制造后電路結構的 “反向建模” 。 |

右側流程:Schematic路徑(從Verilog到原理圖網表)

|

階段 |

步驟名稱 |

輸入 |

輸出 |

使用工具 / 模塊 |

關鍵說明 |

|

1 |

Schematic (.v netlist) |

Verilog 格式的功能網表(Functional Netlist) |

原始設計意圖網表 |

邏輯設計工具、EDA綜合工具 |

- 用 Verilog HDL 描述電路的邏輯功能和模塊結構。 |

|

由設計人員編寫或由邏輯綜合工具生成(如 Design Compiler) |

(如 Design Compiler) |

- 是 “行為級” 或 “結構級” 電路模型。 |

|||

|

|

|

- 通常不包含幾何信息,僅描述邏輯功能。 |

|||

|

|

|

- 是設計者設計意圖的起點。 |

|||

|

2 |

ICV Nettran(網表轉換) |

Verilog 網表 |

Spice / ICV 格式的等效網表 |

IC Validator (ICV) 中的 Nettran 模塊 |

-將 Verilog 網表轉換為 LVS 工具能識別的格式(Spice或ICV格式)。 |

|

轉換規則(Nettran Rule File) |

- 提取邏輯器件(如MOSFET、NAND門等)結構。 |

||||

|

|

- 生成具有器件及連線描述、與版圖網表結構一致的形式。 |

||||

|

|

- 關鍵在于統一 “語法語義” 供LVS比對。 |

||||

|

3 |

Spice ICV Netlist(等效網表) |

轉換后的 Spice 或 ICV 網表格式 |

原理圖等效網表(Reference Netlist) |

LVS 工具讀取該網表參與比對 |

- 結構上與從GDS提取出的Layout Netlist一致或接近。 |

|

(兼容布局提取網表) |

- 包含器件、節點、端口、子模塊調用信息。 |

||||

|

|

- 用于與Layout網表進行逐一比對(器件、連線等)。 |

||||

|

|

- 是 “設計意圖” 的結構映射形式。 |

中間部分:比對過程

1. LVS Compare(LVS 比對)

在這個階段,工具會將“提取網表”和“原理圖網表”進行逐一比對。

比對內容包括:

器件數量是否一致(如多少個NMOS、PMOS等);

器件類型是否一致;

網絡連線是否一致;

器件連接方式、端口命名、子模塊調用是否匹配;

等效性文件中定義的Cell匹配是否正確。

若比對全部通過,則稱為LVS clean;否則將生成詳細錯誤報告供調試使用。

最終輸出:LVS 結果數據庫

2. LVS Result Database(LVS結果數據庫)

這是 LVS 工具生成的結果文件,包含:

比對是否通過(Clean 或 Failed);

不匹配的器件或網絡詳情;

等效點(Equivalence Point)文件;

錯誤日志及調試建議。

工程師可根據此數據庫中的信息,定位設計或版圖中的差異并進行修正。

在版圖提取步驟中,工具從 GDS 文件中提取出所有器件及其之間的連接信息,生成版圖網表。同時,工具還生成一個等效點文件(Equivalence Point File),用于在比對過程中標識版圖與原理圖之間的匹配點。

在比對步驟中,提取出的版圖網表將與原理圖網表進行詳細比對。若兩個網表完全一致,工具將輸出通過(clean)結果;若存在不一致,則會生成包含錯誤詳情的報告。

在比對過程中,工具主要進行以下方面的檢查:

比較原理圖與版圖中的器件數量是否一致;

比較原理圖與版圖中的網絡(Net)數量是否一致;

比較器件類型是否匹配;

生成比對結果報告。

若存在問題,錯誤報告將列出不匹配的器件、不正確的網絡連接等信息,這對于工程師定位和調試 LVS 問題非常有幫助。常見問題如下:

|

問題類型 |

定義 |

成因 |

LVS報告中的表現 |

備注 |

|

Open(斷開連接) |

設計中本應連接的兩個或多個形狀沒有真正相交或接觸,導致網絡中斷,形成浮空連接。 |

- 相同網絡名的圖形未接觸或重疊 |

- 提取器將一個原理圖網絡識別為兩個或多個版圖網絡 |

浮空連接可能導致芯片嚴重功能故障,是高優先級問題 |

|

- 版圖布線錯誤或缺失 |

- 導致版圖網絡數多于原理圖網絡數 |

|||

|

- 自動布線遺漏 |

- 報告中列出 “斷開的網絡” 和其對應的多個版圖網絡名 |

|||

|

- 單元間Metal未連通 |

|

|||

|

Shorts(短路) |

不同網絡意外連接,導致原本應隔離的網絡互相導通。 |

- 不同網絡的圖形重疊/交叉 |

- 提取器將兩個原理圖網絡識別為一個版圖網絡 |

短路可能在功能測試前被忽視,但會在芯片燒毀或性能異常中暴露 |

|

- LEF缺失routing blockage |

- 導致版圖網絡數小于原理圖網絡數 |

|||

|

- 手動布線或金屬填充出錯 |

- 報告中列出 “合并的短路網絡” 和合并前的網絡名 |

|||

|

- 宏單元內部金屬與外部布線沖突 |

|

|||

|

Missing components(器件缺失) |

LVS 流程中找不到設計中引用的某些單元,導致器件不匹配。 |

-GDS 或 Spice 文件未導入完整 |

- 報告中指出缺失某個單元(如ABC) |

需根據cell的實際功能決定是否必須包含 |

|

- Cell未在LVS使用列表中注冊 |

- LVS 比較失敗,提示 “Missing cells” |

|||

|

- 實例存在但未提供定義 |

|

|||

|

Missing global net connect(全局網絡未連接) |

電源/地網絡(PG net)未正確連接到單元的 PG 引腳。 |

- 未使用 connect_pg_net 命令連接PG網絡 |

- 報告中出現大量 device mismatch 錯誤 |

在設計初始化階段配置PG網絡連接至關重要,否則大量器件都將匹配失敗 |

|

- PG引腳名稱未與設計網絡名稱對應上 |

- 多個單元VDD/GND引腳未連接 |

|||

|

|

|

1.2 核心驗證參數

LVS驗證不僅是比對結構,更關注以下幾個核心參數,確保設計邏輯無誤,制造可行:

器件匹配(Device Matching):包括晶體管、二極管、電阻、電容等器件的類型、尺寸、方向是否準確。如果在版圖中器件未正確實例化或參數不符,可能導致LVS錯誤。

連線與互連(Wiring and Connectivity):確保所有信號線、電源線、地線的連接方式與原理圖一致,避免短路、斷路、串擾等問題,這對于復雜SoC或模擬IC尤為關鍵。

幾何形狀與尺寸(Geometry and Dimensions):檢查器件布局的空間分布和形狀是否合理,是否影響工藝流程或引入電氣性能偏差。

1.3 所用工具與技術

為實現高效、可靠的LVS驗證,業界常用以下先進的EDA工具:

Cadence Virtuoso:專注于模擬與混合信號IC設計,集成原理圖編輯、版圖繪制及LVS驗證功能,適合高精度電路驗證。

Synopsys Hercules:適用于大規模數字或混合電路設計,支持高并行性LVS流程,能快速處理復雜多層金屬結構。

Mentor Calibre:被廣泛用于先進制程的DRC/LVS/PEX流程,具備強大的定制化規則支持與高精度校驗能力,是晶圓代工廠標準支持工具之一。

這些工具往往與流程自動化平臺(如Cadence Innovus、Synopsys ICC)結合使用,實現全流程驗證閉環,大幅提升設計效率與成功率。

1.4 面臨的典型挑戰

隨著制程工藝演進至7nm甚至更先進節點,LVS驗證面臨的挑戰也愈加嚴峻,包括:

• 多電壓域、異構器件引發的跨層次比對復雜性增加。

• 高密度互連結構帶來的連通性混淆與器件重構難度上升。

• 類比電路的器件對稱性和匹配精度驗證需求變高。

• 使用IP核或第三方模塊時,黑盒/灰盒模型驗證策略需要優化處理。

針對這些問題,設計團隊必須采用模塊化驗證策略、層次化比對技術以及腳本自動化手段,提高LVS效率與準確性。

通過嚴謹執行LVS流程,設計團隊不僅能夠在Tape-out之前及時發現并解決設計偏差,避免流片失敗,還能提高設計數據的可信度,為后續工藝仿真、電路優化提供堅實基礎。LVS驗證作為IC設計流程的核心環節之一,已經成為確保設計質量、提升良率、降低風險與縮短產品上市周期的重要保障手段。

2.LVS在半導體制造中的關鍵作用

在競爭激烈、技術迅速演進的半導體行業中,確保設計正確性和提升芯片良率已成為產品能否成功量產的決定性因素。版圖與原理圖一致性檢查(LVS, Layout versus Schematic),正是實現這一目標的重要質量控制環節,其作用貫穿從IC設計驗證到制造交付的全過程。

LVS檢查通過將設計原理圖中的功能描述與實際版圖中實現的器件及其互連結構進行一一比對,確保版圖忠實還原設計意圖。它可以及時發現隱藏在復雜電路結構中的連線錯誤、器件缺失、參數不符或連接歧義等問題,這些問題若在制造階段被發現,將會造成昂貴的流片返工和項目周期延誤。

2.1 LVS對良率與成本的影響

LVS不僅是保障功能正確性的工具,更是控制制造成本、提高產品良率的核心手段:

降低缺陷率:通過在流片前發現版圖錯誤,防止缺陷產品流入生產環節,有效減少芯片返修與報廢,提高整體成品率。

控制制造成本:早期發現并修復問題,能夠避免因邏輯錯誤或互連失誤導致的多次流片,從而顯著節省昂貴的晶圓成本、測試資源和工程人力。

提升產品一致性:LVS驗證有助于確保各批次芯片在功能和性能上的一致性,減少因工藝波動帶來的系統級問題,提升客戶對產品穩定性的信任度。

支撐大規模量產:在先進制程節點和復雜SoC設計中,借助自動化LVS流程,可快速對多個模塊或IP核進行統一驗證,提升驗證效率,支持更大規模、高復雜度的芯片穩定流片。

|

LVS檢查的關鍵優勢 |

對半導體制造的影響 |

|

提升設計完整性 |

降低制造成本 |

|

確保版圖與原理圖在器件、連線、網絡結構上的一致性,避免功能性錯誤進入流片階段 |

通過減少因設計錯誤導致的返工與流片失敗,顯著節省制造資源與時間 |

|

提高良率 |

提升產品質量水平 |

|

減少版圖錯誤帶來的器件失效,提升成品芯片的有效產出比例 |

確保電氣連接正確性,保障芯片在功能、電氣參數上的一致性和可靠性 |

|

降低缺陷率 |

增強企業市場競爭力 |

|

及時發現和修復潛在連接錯誤、器件不匹配等問題,從源頭控制失效風險 |

縮短設計周期、提高一次通過率,加快產品上市速度,提升客戶滿意度 |

2.2 LVS與制造流程的協同價值

LVS不僅僅是一項獨立的設計驗證任務,更是半導體制造流程中與前后工序緊密耦合的橋梁:

|

步驟 |

名稱 |

內容說明 |

目標 |

使用工具 |

注意事項 |

|

1 |

Design Specifications |

設計起點,由系統/架構工程師提供芯片目標參數,如功能、電壓、頻率、功耗、I/O要求等 |

- 明確功能需求(如增益、帶寬、噪聲) |

無工具依賴(文檔或模板形式) |

- 規范需無歧義,避免設計返工 |

|

(設計規格) |

- 定義技術規格(CMOS工藝、平臺) |

- 內容必須詳細全面 |

|||

|

|

- 指導原理圖和版圖設計 |

|

|||

|

2 |

Schematic Capture |

使用EDA工具繪制電路連接圖,實現功能模塊 |

- 實現功能結構 |

Cadence Virtuoso、LTspice、Mentor Graphics |

- 管腳命名需統一一致 |

|

(原理圖繪制) |

- 定義引腳連接與網絡關系 |

- 保證連接正確、無懸空或短路 |

|||

|

3 |

Create Symbol |

將模塊電路生成抽象符號(Symbol)以供系統層級調用 |

- 抽象電路模塊以便復用 |

Cadence Virtuoso Symbol Editor |

- 端口順序與原理圖一致 |

|

(生成符號) |

- 用于更大系統中的層級集成 |

- 命名清晰、方向標識準確 |

|||

|

4 |

Simulation |

進行DC、AC、Transient仿真,驗證電路性能 |

- 驗證電路功能是否符合設計規格 |

Spectre、HSPICE、Eldo、LTspice |

- 使用PDK中提供的精確模型 |

|

(電路仿真) |

- 分析關鍵指標(增益、帶寬、功耗、噪聲、失真等) |

- 仿真數據需歸檔,便于評審和追溯 |

|||

|

5 |

Layout |

將電路轉換為物理幾何圖形,準備制造 |

- 滿足電氣與工藝規范 |

Cadence Virtuoso Layout Editor |

- 遵循Foundry工藝規則(線寬、間距) |

|

(版圖設計) |

- 考慮面積、寄生、電源分布等 |

- 考慮匹配、寄生、電容電阻效應 |

|||

|

6 |

Design Rule Check (DRC) |

自動檢查版圖是否違反工藝設計規則 |

- 檢查版圖與工藝規則是否一致 |

Mentor Calibre DRC、Cadence Assura、Synopsys ICV |

- 報錯必須修復直至DRC通過 |

|

(設計規則檢查) |

- 避免制造錯誤 |

- 是后續步驟的前置條件 |

|||

|

7 |

Extraction |

提取電路中的RC寄生,生成帶寄生的網表 |

- 獲取真實性能影響因素 |

Calibre xRC、Assura RCX、ICV |

- 模型需準確反映金屬、電介質、過孔等 |

|

(寄生參數提取) |

- 為LVS與仿真準備輸入 |

- 可選擇提取層級控制仿真效率 |

|||

|

8 |

Layout vs. Schematic (LVS) |

比較提取網表與原理圖網表的一致性 |

- 驗證功能一致性 |

Calibre LVS、Assura LVS、ICV LVS |

- 常見問題:短路、開路、器件漏繪、網絡不一致 |

|

(版圖與原理圖對比) |

- 檢查器件、連線完整性 |

- 調試需結合報錯提示與物理版圖 |

|||

|

9 |

Post-Layout Simulation |

使用PEX網表進行仿真,評估寄生影響 |

- 驗證寄生對性能的影響 |

Spectre + PEX Netlist、HSPICE + Extracted Netlist |

- 若性能下降需調整版圖或重新布局 |

|

(布局后仿真) |

- 判斷是否仍滿足規格要求 |

- 是驗證制造一致性的重要環節 |

與DRC(Design Rule Check)協同:先執行DRC確保物理規則合規,再通過LVS驗證功能一致性,構建完整的制造準備驗證鏈條。

與寄生參數提取(PEX)集成:在LVS完成器件與連接一致性驗證之后,通過PEX提取寄生元件,進一步提升后仿真精度,優化性能預測。

與工藝模擬與測試反饋閉環聯動:部分代工廠會將實測缺陷反饋到設計端,并通過LVS工具溯源問題根本原因,優化設計規范,形成制造質量提升閉環。

2.3 應對先進制程挑戰的LVS發展趨勢

隨著芯片設計進入7nm、5nm甚至更先進節點,LVS驗證面臨更高復雜度和更嚴苛的性能要求。為應對挑戰,LVS正呈現以下發展趨勢:

• 支持異構集成與多芯粒(chiplet)架構:驗證跨芯片模塊互聯一致性,確保整體系統可靠運行。

• 增強AI輔助診斷與可視化調試能力:借助機器學習自動識別典型錯誤模式,提升調試效率。

• 強化對模擬/射頻/高速IO等復雜器件結構的建模與對比能力:增強匹配度與靈敏度。

• 與數字孿生建模、PPA協同優化集成:讓LVS結果參與性能功耗面積(Power, Performance, Area)決策過程。

總 結

LVS不僅是確保IC設計質量的防線,更是提升制造良率、優化成本結構、縮短項目周期的戰略性技術手段。通過將LVS深度嵌入整個芯片開發和制造流程,半導體企業能夠在降低風險的同時,充分發揮設計潛力,打造高性能、高可靠性、高性價比的芯片產品,從而在激烈的市場競爭中穩占優勢。

參 考:

1.What is Layout vs. Schematic (LVS) check, and why is it essential?

2.Layout versus Schematic (LVS) Debug

3.VLSI Design Quick Guide

來源:芯片技術與工藝