您當前的位置:檢測資訊 > 科研開發

嘉峪檢測網 2025-08-17 19:32

TSV TGV

——從“把芯片疊起來”到“把玻璃變成芯片高速公路”

“如果把摩爾定律比作一條越走越窄的高速公路,TSV 和 TGV 就是正在修建的立體高架橋。”

——IMEC 3D 集成項目總監 Eric Beyne,2024 IEEE ECTC

一、為什么今天的芯片“必須”打洞?

1. 算力需求爆炸

• 訓練 GPT-4 的 1.8 T 參數模型需要 25 萬顆 A100 并行,功耗 50 MW——傳統 2D 封裝已無法承受 I/O 數量與互連長度的指數級增長。

2. 物理極限逼近

• 5 nm 以下節點繼續微縮,晶體管成本不降反升,3D 集成成為“More than Moore”的核心賽道。

3. 先進封裝成為第二摩爾定律

• Yole 2024 報告顯示,3D 封裝市場 CAGR 18%,2028 年將達 290 億美元,其中 TSV & TGV 占 42% 價值量。

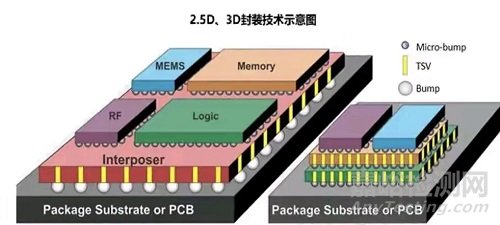

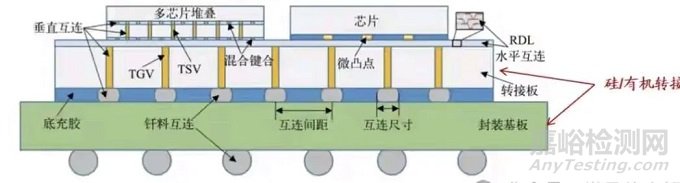

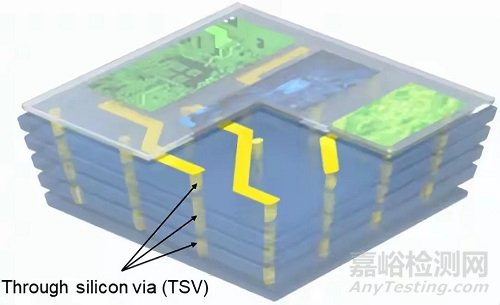

二、TSV:硅片里的“垂直地鐵”

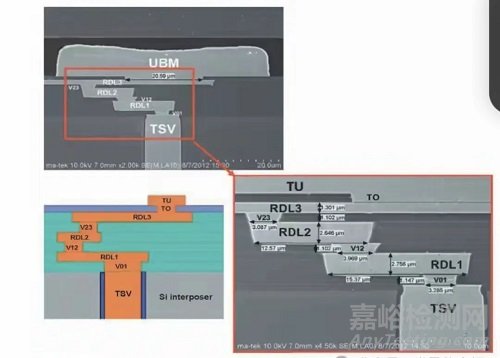

2.1 結構剖面

• 典型尺寸:孔徑 5–20 µm,深度 50–200 µm,深寬比 10:1–20:1

• 四層三明治:SiO? 絕緣層 → Ti/Ta 阻擋層 → Cu 種子層 → Cu 填充柱

2.2 三種工藝流“誰先用刀打孔”

• Via-First:FEOL 前打洞,可高溫退火,成本低,但限制后續晶體管工藝。

• Via-Middle:晶體管完成后、BEOL 之前,平衡熱預算與對準精度,主流用于 HBM

• Via-Last:BEOL 后打洞,兼容最成熟節點,但深孔刻蝕難度最大,CoWoS-S 采用。

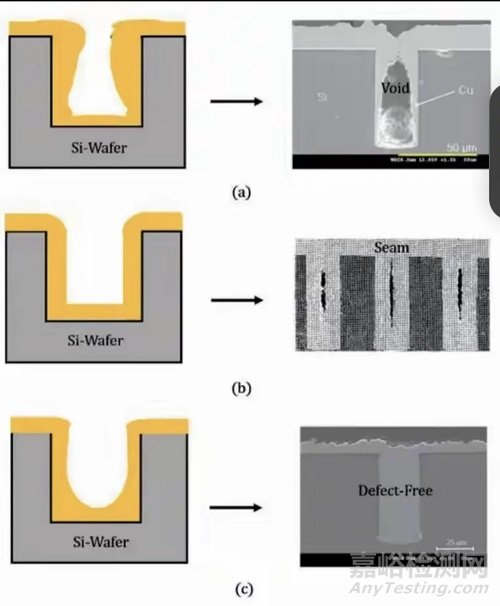

2.3 金屬填充的四重奏

• Sub-conformal:空洞多,早期研究品。

• Conformal:留一條中心縫,主流量產。

• Super-conformal:無縫,但電鍍液添加劑昂貴,用于高頻射頻器件。

• Bottom-up:完全無空洞,電鍍時間縮短 30%,臺積電 SoIC 已導入。

2.4 可靠性“三座大山”(質量風險)

• Cu-Si CTE 差異 16.5 → 2.6 ppm/℃ → 熱循環 1000× 后微裂

• 應力誘發載流子遷移 (SM)——斯坦福大學 2023 發現 200 ℃ 下 MTTF 下降 3×

• 漏電路徑:SiO? 擊穿 < 4 MV/cm 時,tdDB 模型預測 10 年壽命需厚度 ≥ 0.5 µm

三、TGV:玻璃基板上的“光之橋”

3.1 材料優勢

• 電阻率 10¹? Ω·cm,比 Si 高 8 個數量級,RF 損耗 < 0.1 dB/mm@60 GHz

• CTE 3.3 ppm/℃,與 Cu 差距縮小 5×,減少熱應力

• 透明性 → 激光一次性鉆孔 1000 孔,產能提升 10×(LPKF Vitrion 5000 數據)

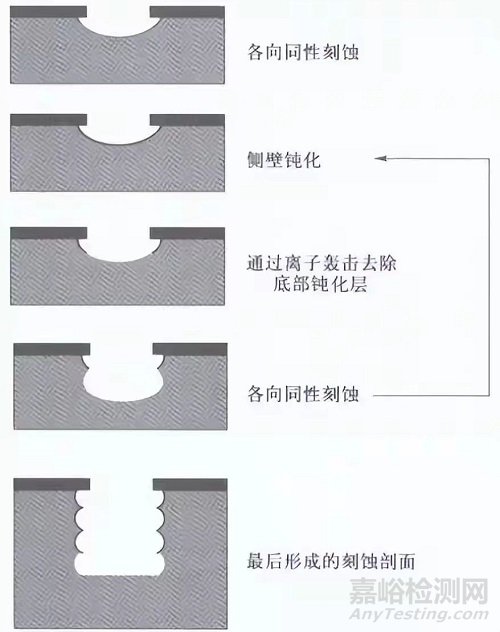

3.2 Bosch工藝

Bosch工藝,也稱為交替側壁鈍化深層硅蝕刻工藝,是一種用于制造高深寬比微結構的先進技術,廣泛應用于微機電系統(MEMS)和深硅刻蝕領域。Bosch工藝的影響可以從多個方面進行考慮:

3.3 應用落地

• 高通 2024 發布的 Snapdragon X Elite RF 模組:TGV 玻璃轉接板集成 IPD 濾波器,厚度減 30%,插損降 1.2 dB。

• 三星電機 2025 路線圖中,TGV 用于 RDL-Interposer,替代 CoWoS-R 的昂貴硅中介層,目標成本下降 40%。

四、TSV vs TGV:一張圖看懂選擇邏輯

• 當信號 > 40 Gbps、功耗 > 200 W:優先 TSV,熱膨脹匹配 + 細間距。

• 當頻率 > 60 GHz、成本敏感:優先 TGV,低損耗 + 大尺寸玻璃。

• 兩者混合:AMD MI300 采用 TSV 堆疊 HBM + TGV 玻璃橋接 I/O,整體封裝厚度從 2.5 mm 降到 1.7 mm。

五、質量與可靠性的“暗礁”

5.1 TSV 典型失效模式

• 微裂檢測:IR-LST(紅外光致發光)掃描,可發現 < 5 µm 裂紋,D0 提升 15%。

• Cu pumping:熱循環后 Cu 柱凸出 0.5–1 µm,導致 RDL 剝離——采用 TaN 擴散阻擋層 + 低應力 Cu 電鍍添加劑,失效概率降低 80%。

5.2 TGV 特有挑戰

• 激光熱損傷:孔壁出現 2–3 µm 重鑄層,介電強度降低 20%,需 CO? 激光 + 濕法蝕刻復合工藝。

• 玻璃-金屬結合力:PI 增粘層 + Ar 等離子體處理,剝離強度從 0.3 N/cm 提升到 1.2 N/cm(Fraunhofer IZM 2024 數據)。

六、未來展望:硅-玻璃共封裝

1. 0.5 µm Pitch TSV:IMEC 已演示 0.5 µm 直徑、深寬比 25:1 的“TSV-last”工藝,預計 2027 年用于 3 nm + 3D V-Cache。

2. TGV 光電共封裝:Intel 2025 計劃用 TGV 玻璃做 CPO(Co-packaged Optics)基板,單通道 200 Gbps,功耗 < 5 pJ/bit。

3. 可持續制造:玻璃可循環熔化 5 次,碳足跡比硅低 35%,符合歐盟 2030 半導體綠色制造路線。

結語

從“在硅片上挖深井”到“在玻璃上雕光路”,TSV 與 TGV 代表了半導體產業向第三維度的集體遷徙。它們不僅是先進封裝的基石,更是 AI 算力持續指數級增長的物理前提。下一次,當你看到 H100 的 80 GB HBM3 以 3.2 TB/s 吞吐時,別忘了——那其實是成千上萬根“硅銅地鐵”與“玻璃光橋”在并肩工作。

參考文獻

[1] Yole Développement, 3D & Advanced Packaging Technology Market Monitor, 2024.

[2] IEEE ECTC 2024 Keynote, “Scaling 3D Integration beyond 1 µm Pitch”.

[3] IMEC, “Reliability of Cu TSV in 3 nm Technology Node”, 2023.

[4] Intel, “Co-Packaged Optics with TGV Glass Substrate”, OFC 2025.

來源:芯芯有我